- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄8238 > SN74ABT162501DLR (Texas Instruments)IC UNIV BUS TXRX 18BIT 56SSOP PDF資料下載

參數(shù)資料

| 型號(hào): | SN74ABT162501DLR |

| 廠商: | Texas Instruments |

| 文件頁(yè)數(shù): | 1/10頁(yè) |

| 文件大小: | 0K |

| 描述: | IC UNIV BUS TXRX 18BIT 56SSOP |

| 標(biāo)準(zhǔn)包裝: | 1 |

| 系列: | 74ABT |

| 邏輯類型: | 通用總線收發(fā)器 |

| 電路數(shù): | 18 位 |

| 輸出電流高,低: | 32mA,64mA; 12mA,12mA |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 56-BSSOP(0.295",7.50mm 寬) |

| 供應(yīng)商設(shè)備封裝: | 56-SSOP |

| 包裝: | 標(biāo)準(zhǔn)包裝 |

| 產(chǎn)品目錄頁(yè)面: | 926 (CN2011-ZH PDF) |

| 其它名稱: | 296-1027-6 |

SN54ABT162501, SN74ABT162501

18-BIT UNIVERSAL BUS TRANSCEIVERS

WITH 3-STATE OUTPUTS

SCBS243E – SEPTEMBER 1992 – REVISED FEBRUARY 1999

1

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

D Members of the Texas Instruments

Widebus

Family

D B-Port Outputs Have Equivalent 25-

Series Resistors, So No External Resistors

Are Required

D State-of-the-Art EPIC-ΙΙB BiCMOS Design

Significantly Reduces Power Dissipation

D UBT (Universal Bus Transceiver)

Combines D-Type Latches and D-Type

Flip-Flops for Operation in Transparent,

Latched, or Clocked Mode

D Typical VOLP (Output Ground Bounce)

< 0.8 V at VCC = 5 V, TA = 25°C

D High-Impedance State During Power Up

and Power Down

D Flow-Through Architecture Optimizes PCB

Layout

D Latch-Up Performance Exceeds 500 mA

Per JESD 17

D ESD Protection Exceeds 2000 V Per

MIL-STD-883, Method 3015; Exceeds 200 V

Using Machine Model (C = 200 pF, R = 0)

D Package Options Include Plastic Shrink

Small-Outline (DL) and Thin Shrink

Small-Outline (DGG) Packages and 380-mil

Fine-Pitch Ceramic Flat (WD) Package

Using 25-mil Center-to-Center Spacings

description

These 18-bit universal bus transceivers consist of

storage elements that can operate either as

D-type latches or D-type flip-flops to allow data

flow in transparent or clocked modes.

Data flow in each direction is controlled by output-enable (OEAB and OEBA), latch-enable (LEAB and LEBA),

and clock (CLKAB and CLKBA) inputs. For A-to-B data flow, the device operates in the transparent mode when

LEAB is high. When LEAB is low, the A data is latched if CLKAB is held at a high or low logic level. If LEAB is

low, the A data is stored in the latch/flip-flop on the low-to-high transition of CLKAB. When OEAB is high, the

outputs are active. When OEAB is low, the outputs are in the high-impedance state.

Data flow for B to A is similar to that of A to B but uses OEBA, LEBA, and CLKBA. The output enables are

complementary (OEAB is active high and OEBA is active low).

The B-port outputs, which are designed to source or sink up to 12 mA, include equivalent 25-

series resistors

to reduce overshoot and undershoot.

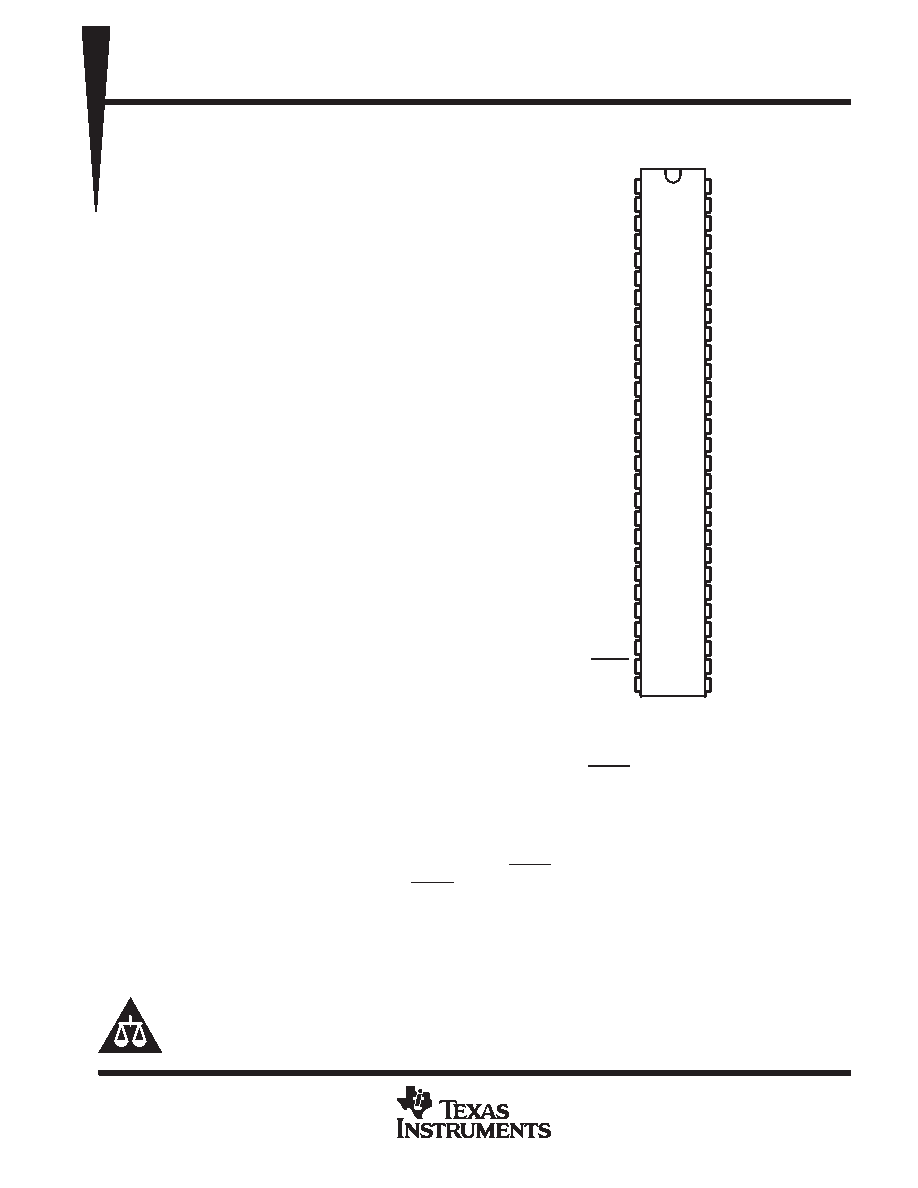

SN54ABT162501 ...WD PACKAGE

SN74ABT162501 . . . DGG OR DL PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

OEAB

LEAB

A1

GND

A2

A3

VCC

A4

A5

A6

GND

A7

A8

A9

A10

A11

A12

GND

A13

A14

A15

VCC

A16

A17

GND

A18

OEBA

LEBA

GND

CLKAB

B1

GND

B2

B3

VCC

B4

B5

B6

GND

B7

B8

B9

B10

B11

B12

GND

B13

B14

B15

VCC

B16

B17

GND

B18

CLKBA

GND

Copyright

1999, Texas Instruments Incorporated

UNLESS OTHERWISE NOTED this document contains PRODUCTION

DATA information current as of publication date. Products conform to

specifications per the terms of Texas Instruments standard warranty.

Production processing does not necessarily include testing of all

parameters.

Widebus, EPIC-

ΙΙB, and UBT are trademarks of Texas Instruments Incorporated.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of

Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| GTLP16612MTD | IC UNIV BUS TXRX 18BIT 56TSSOP |

| GTLP16612MTDX | IC UNIV BUS TXRX 18BIT 56TSSOP |

| PI74AVC+16836AE | IC UNIV BUS DVR 20BIT 56TSSOP |

| 74LCX16501MTD | TXRX 18BIT UNIV BUS LV 56TSSOP |

| 74LCX16500MTD | TXRX 18BIT UNIV BUS LV 56TSSOP |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74ABT162601 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:18-BIT UNIVERSAL BUS TRANSCEIVERS WITH 3-STATE OUTPUTS |

| SN74ABT162601DGG | 功能描述:IC UNIV BUS TXRX 18BIT 56TSSOP RoHS:是 類別:集成電路 (IC) >> 邏輯 - 通用總線函數(shù) 系列:74ABT 產(chǎn)品變化通告:Product Discontinuation 09/Dec/2010 標(biāo)準(zhǔn)包裝:1,500 系列:74AVC 邏輯類型:通用總線驅(qū)動(dòng)器 輸入數(shù):- 電路數(shù):18 位 輸出電流高,低:12mA,12mA 電源電壓:1.65 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:56-TFSOP(0.240",6.10mm 寬) 供應(yīng)商設(shè)備封裝:56-TSSOP 包裝:帶卷 (TR) |

| SN74ABT162601DGGR | 功能描述:通用總線函數(shù) 18-Bit Univ Bus Trncvr W/3-St Otpt RoHS:否 制造商:Texas Instruments 邏輯類型:CMOS 邏輯系列:74VMEH 電路數(shù)量:1 開(kāi)啟電阻(最大值): 傳播延遲時(shí)間:10.1 ns 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大工作溫度:+ 85 C 最小工作溫度:0 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74ABT162601DL | 功能描述:通用總線函數(shù) 18-Bit Univ Bus Trncvr W/3-St Otpt RoHS:否 制造商:Texas Instruments 邏輯類型:CMOS 邏輯系列:74VMEH 電路數(shù)量:1 開(kāi)啟電阻(最大值): 傳播延遲時(shí)間:10.1 ns 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大工作溫度:+ 85 C 最小工作溫度:0 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| SN74ABT162601DLG4 | 功能描述:通用總線函數(shù) 18-Bit Univ Bus Trncvr W/3-St Otpt RoHS:否 制造商:Texas Instruments 邏輯類型:CMOS 邏輯系列:74VMEH 電路數(shù)量:1 開(kāi)啟電阻(最大值): 傳播延遲時(shí)間:10.1 ns 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大工作溫度:+ 85 C 最小工作溫度:0 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。