- 您現在的位置:買賣IC網 > PDF目錄383851 > SY100E154JCTR (MICREL INC) 5-BIT 2:1 MUX-LATCH PDF資料下載

參數資料

| 型號: | SY100E154JCTR |

| 廠商: | MICREL INC |

| 元件分類: | 通用總線功能 |

| 英文描述: | 5-BIT 2:1 MUX-LATCH |

| 中文描述: | 100E SERIES, LOW LEVEL TRIGGERED D LATCH, COMPLEMENTARY OUTPUT, PQCC28 |

| 封裝: | PLASTIC, LCC-28 |

| 文件頁數: | 1/4頁 |

| 文件大小: | 61K |

| 代理商: | SY100E154JCTR |

I

750ps max. LEN to output

I

Extended 100E V

EE

range of –4.2V to –5.5V

I

700ps max. D to output

I

Differential outputs

I

Asynchronous Master Reset

I

Dual latch-enables

I

Fully compatible with industry standard 10KH,

100K ECL levels

I

Internal 75K

input pulldown resistors

I

Fully compatible with Motorola MC10E/100E154

I

Available in 28-pin PLCC package

FEATURES

5-BIT 2:1

MUX-LATCH

The SY10/100E154 offer five 2:1 multiplexers followed

by latches with differential outputs, designed for use in

new, high-performance ECL systems. The two external

Latch-Enable signals (LEN

1

, LEN

2

) are gated through a

logical OR operation before use as control for the five

latches. When both LEN

1

and LEN

2

are at a logic LOW, the

latches are transparent, thus presenting the data from the

multiplexers at the output pins. If either LEN

1

or LEN

2

(or

both) are at a logic HIGH, the outputs are latched.

The multiplexer operation is controlled by the SEL(Select)

signal which selects one of the two bits of input data at each

mux to be passed through.

The MR (Master Reset) signal operates asynchronously

to make all Q outputs go to a logic LOW.

DESCRIPTION

Rev.: C

Issue Date: February, 1998

Amendment: /1

SY10E154

SY100E154

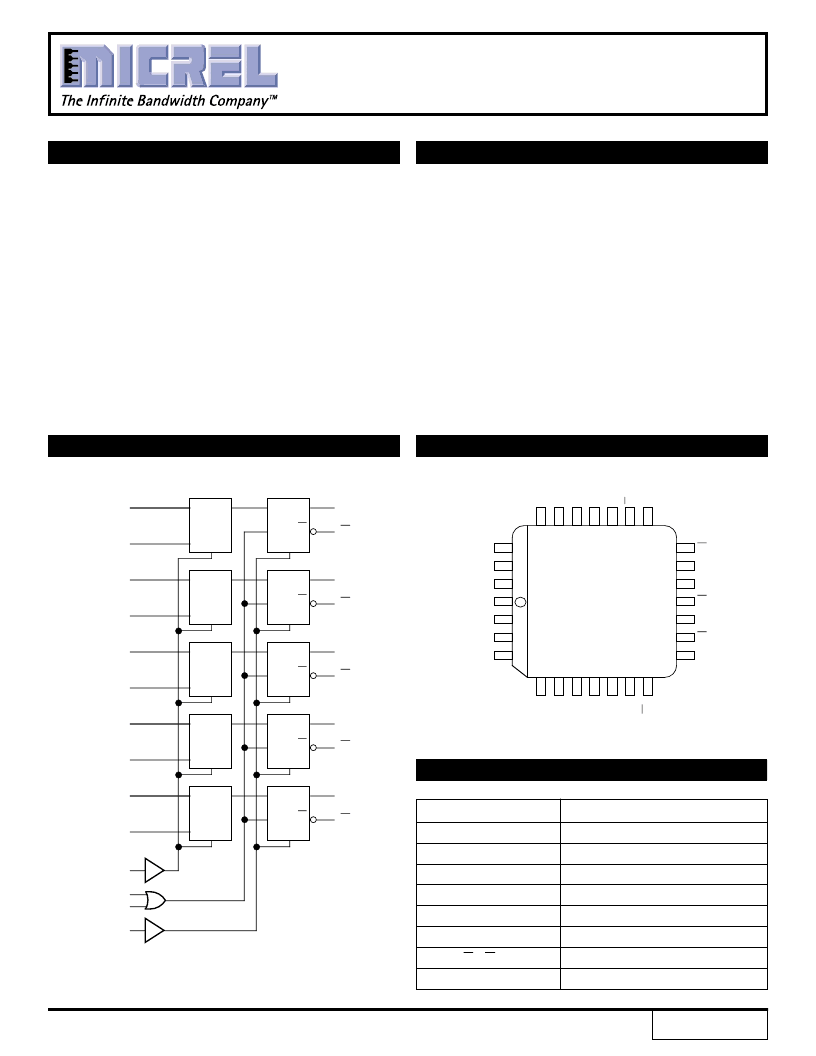

BLOCK DIAGRAM

Pin

Function

D

0a

–D

4a

Input Data a

D

0b

–D

4b

Input Data b

SEL

Data Select Input

LEN

1

, LEN

2

Latch Enables

MR

Master Reset

Q

0

–Q

4

True Outputs

Q

0

–Q

4

Inverted Outputs

V

CCO

V

CC

to Output

PIN CONFIGURATION

PIN NAMES

V

EE

MR

SEL

LEN

1

LEN

2

D

0a

D

0b

Q

4

26

27

28

1

2

3

4

18

17

16

15

14

13

12

25 24 23 22 21 20 19

5

6

7

8

9

10 11

Q

0

Q

0

Q

3

Q

3

V

CC

Q

2

Q

2

Q

1

Q

1

V

C

PLCC

TOP VIEW

J28-1

D

4

D

3

D

3

V

C

D

2

D

2

D

1

D

1

D

4

Q

4

MR

D

R

D

0a

LEN

1

LEN

2

Q

E

N

Q

MUX

SEL

SEL

D

0b

D

R

D

1a

Q

E

N

Q

MUX

D

1b

D

R

D

2a

Q

E

N

Q

MUX

D

2b

D

R

D

3a

Q

E

N

Q

MUX

D

3b

D

R

D

4a

Q

0

Q

0

Q

1

Q

1

Q

2

Q

2

Q

3

Q

3

Q

4

Q

4

Q

E

N

Q

MUX

D

4b

SEL

SEL

SEL

SEL

1

相關PDF資料 |

PDF描述 |

|---|---|

| SY10E154 | 5-BIT 2:1 MUX-LATCH |

| SY10E154JC | 5-BIT 2:1 MUX-LATCH |

| SY10E154JCTR | 5-BIT 2:1 MUX-LATCH |

| SY100E154 | 5-BIT 2:1 MUX-LATCH |

| SY100E154JZ | 5-BIT 2:1 MUX-LATCH |

相關代理商/技術參數 |

參數描述 |

|---|---|

| SY100E154JZ | 功能描述:IC MUX-LATCH 5BIT 2:1 28-PLCC RoHS:是 類別:集成電路 (IC) >> 邏輯 - 信號開關,多路復用器,解碼器 系列:100E 標準包裝:1 系列:74LVC 類型:解碼器/多路分解器 電路:1 x 2:4 獨立電路:2 輸出電流高,低:24mA,24mA 電壓電源:單電源 電源電壓:1.65 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:16-SOIC(0.209",5.30mm 寬) 供應商設備封裝:16-SO 包裝:Digi-Reel® 其它名稱:296-28947-6 |

| SY100E154JZ TR | 功能描述:IC MUX-LATCH 5BIT 2:1 28PLCC RoHS:是 類別:集成電路 (IC) >> 邏輯 - 信號開關,多路復用器,解碼器 系列:100E 標準包裝:25 系列:74HC 類型:解碼器 電路:1 x 2:4 獨立電路:2 輸出電流高,低:5.2mA,5.2mA 電壓電源:單電源 電源電壓:2 V ~ 6 V 工作溫度:-40°C ~ 85°C 安裝類型:通孔 封裝/外殼:16-DIP(0.300",7.62mm) 供應商設備封裝:16-DIP 包裝:管件 |

| SY100E154JZTR | 制造商:MICREL 制造商全稱:Micrel Semiconductor 功能描述:5-BIT 2:1 MUX-LATCH |

| SY100E155 | 制造商:MICREL 制造商全稱:Micrel Semiconductor 功能描述:6-BIT 2:1 MUX-LATCH |

| SY100E155JC | 功能描述:IC MUX-LATCH 6-BIT 2:1 28-PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - 信號開關,多路復用器,解碼器 系列:100E 標準包裝:25 系列:74HC 類型:解碼器 電路:1 x 2:4 獨立電路:2 輸出電流高,低:5.2mA,5.2mA 電壓電源:單電源 電源電壓:2 V ~ 6 V 工作溫度:-40°C ~ 85°C 安裝類型:通孔 封裝/外殼:16-DIP(0.300",7.62mm) 供應商設備封裝:16-DIP 包裝:管件 |

發布緊急采購,3分鐘左右您將得到回復。