參數資料

| 型號: | SY100S331JC TR |

| 廠商: | Micrel Inc |

| 文件頁數: | 1/6頁 |

| 文件大小: | 0K |

| 描述: | IC FLIP FLOP TRIPLE D 28-PLCC |

| 標準包裝: | 750 |

| 系列: | 100S |

| 功能: | 主復位 |

| 類型: | D 型總線 |

| 輸出類型: | 差分 |

| 元件數: | 3 |

| 每個元件的位元數: | 1 |

| 頻率 - 時鐘: | 800MHz |

| 延遲時間 - 傳輸: | 300ps |

| 觸發器類型: | 正邊沿 |

| 電源電壓: | 4.2 V ~ 5.5 V |

| 工作溫度: | 0°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 28-LCC(J 形引線) |

| 包裝: | 帶卷 (TR) |

| 其它名稱: | SY100S331JCTR SY100S331JCTR-ND |

1

SY100S331

Micrel, Inc.

M9999-060910

hbwhelp@micrel.com or (408) 955-1690

TRIPLE D

FLIP-FLOP

SY100S331

■ Max.togglefrequencyof800MHz

■ Differentialoutputs

■ IEEmin.of–80mA

■ Industrystandard100KECLlevels

■ Extendedsupplyvoltageoption:

VEE=–4.2Vto–5.5V

■ Voltageandtemperaturecompensationforimproved

noiseimmunity

■ Internal75kinputpull-downresistors

■ 150%fasterthanFairchild

■ 40%lowerpowerthanFairchild

■ FunctionandpinoutcompatiblewithFairchildF100K

■ Availablein28-pinPLCCpackage

FEATURES

DESCRIPTION

TheSY100S331offersthreeD-type,edge-triggeredmaster/

slave flip-flops with true and complement outputs, designed

for use in high-performance ECL systems. Each flip-flop is

controlled by a common clock (CPc), as well as its own clock

pulse (CPn). The resultant clock signal controlling the flip-flop

is the logical OR operation of these two clock signals. Data

entersthemasterwhenbothCPc andCPn areLOWandenters

the slave on the rising edge of either CPc or CPn (or both).

Additional control signals include Master Set (MS) and

Master Reset (MR) inputs. Each flip-flop also has its own

Direct Set (SDn) and Direct Clear (CDn) signals. The MR, MS,

SDn and DCn signals override the clock signals. The inputs

on this device have 75k pull-down resistors.

Rev.: I

Amendment: /0

Issue Date: June 2010

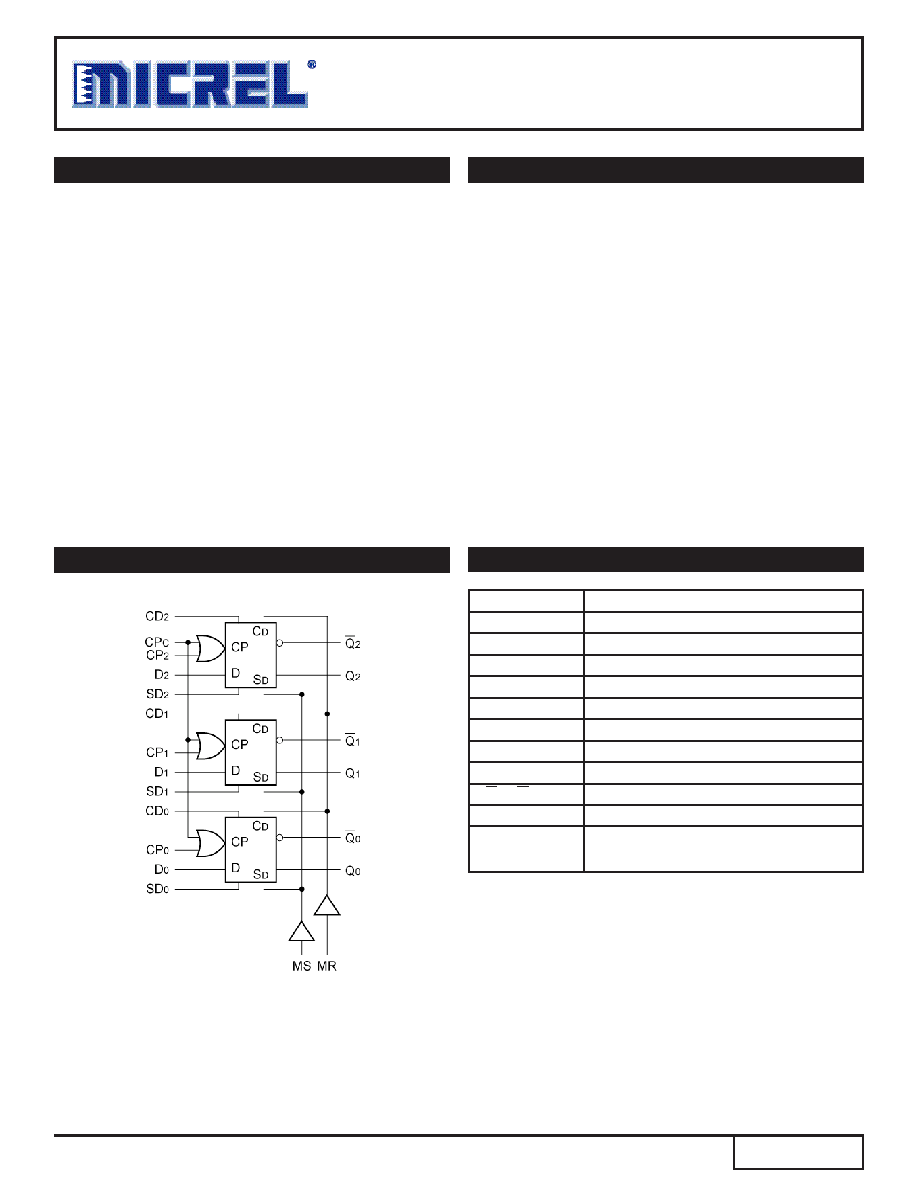

BLOCKDIAGRAM

Pin

Function

CP0 – CP2

Individual Clock Inputs

CPc

Common Clock Input

D0 – D2

Data Inputs

CD0 – CD2

Individual Direct Clear Inputs

SDn

Individual Direct Set Inputs

MR

Master Reset Input

MS

Master Set Input

Q0 – Q2

Data Outputs

Q0 – Q2

Complementary Data Outputs

VEES

VEE Substrate

VCCA

VCCO for ECL Outputs

PINNAMES

相關PDF資料 |

PDF描述 |

|---|---|

| VI-25P-MV-F4 | CONVERTER MOD DC/DC 13.8V 150W |

| SY100S331JC | IC FLIP FLOP TRIPLE D 28-PLCC |

| MS27468T23B35PBLC | CONN HSG RCPT 100POS JAM NUT PIN |

| MS27484E12A35PLC | CONN HSG PLUG 22POS STRGHT PIN |

| MS3456W20-18BZ | CONN HSG PLUG 9POS STRGHT SCKT |

相關代理商/技術參數 |

參數描述 |

|---|---|

| SY100S331JZ | 功能描述:觸發器 Triple D Flip-Flop (Lead Free) RoHS:否 制造商:Texas Instruments 電路數量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| SY100S331JZ TR | 功能描述:觸發器 Triple D Flip-Flop (Lead Free) RoHS:否 制造商:Texas Instruments 電路數量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| SY100S336AFC | 功能描述:IC COUNTER/SHIFT REG 24-CERPAC+G RoHS:否 類別:集成電路 (IC) >> 邏輯 - 專用邏輯 系列:100S 產品變化通告:Product Discontinuation 25/Apr/2012 標準包裝:1,500 系列:74SSTV 邏輯類型:DDR 的寄存緩沖器 電源電壓:2.3 V ~ 2.7 V 位數:14 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:48-TFSOP(0.240",6.10mm 寬) 供應商設備封裝:48-TSSOP 包裝:帶卷 (TR) |

| SY100S336AJC | 功能描述:IC COUNTER/SHIFT REG 28-PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - 專用邏輯 系列:100S 產品變化通告:Product Discontinuation 25/Apr/2012 標準包裝:1,500 系列:74SSTV 邏輯類型:DDR 的寄存緩沖器 電源電壓:2.3 V ~ 2.7 V 位數:14 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:48-TFSOP(0.240",6.10mm 寬) 供應商設備封裝:48-TSSOP 包裝:帶卷 (TR) |

| SY100S336FC | 功能描述:IC COUNTER/SHIFT REG 24-CERPACK RoHS:否 類別:集成電路 (IC) >> 邏輯 - 專用邏輯 系列:100S 產品變化通告:Product Discontinuation 25/Apr/2012 標準包裝:1,500 系列:74SSTV 邏輯類型:DDR 的寄存緩沖器 電源電壓:2.3 V ~ 2.7 V 位數:14 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:48-TFSOP(0.240",6.10mm 寬) 供應商設備封裝:48-TSSOP 包裝:帶卷 (TR) |

發布緊急采購,3分鐘左右您將得到回復。