- 您現在的位置:買賣IC網 > PDF目錄383855 > SY100S336AFC (MICREL INC) ENHANCED 4-STAGE COUNTER/SHIFT REGISTER PDF資料下載

參數資料

| 型號: | SY100S336AFC |

| 廠商: | MICREL INC |

| 元件分類: | 通用總線功能 |

| 英文描述: | ENHANCED 4-STAGE COUNTER/SHIFT REGISTER |

| 中文描述: | 100S SERIES, SYN POSITIVE EDGE TRIGGERED 4-BIT BIDIRECTIONAL BINARY COUNTER, CQFP24 |

| 封裝: | CERPACK-24 |

| 文件頁數: | 1/9頁 |

| 文件大小: | 149K |

| 代理商: | SY100S336AFC |

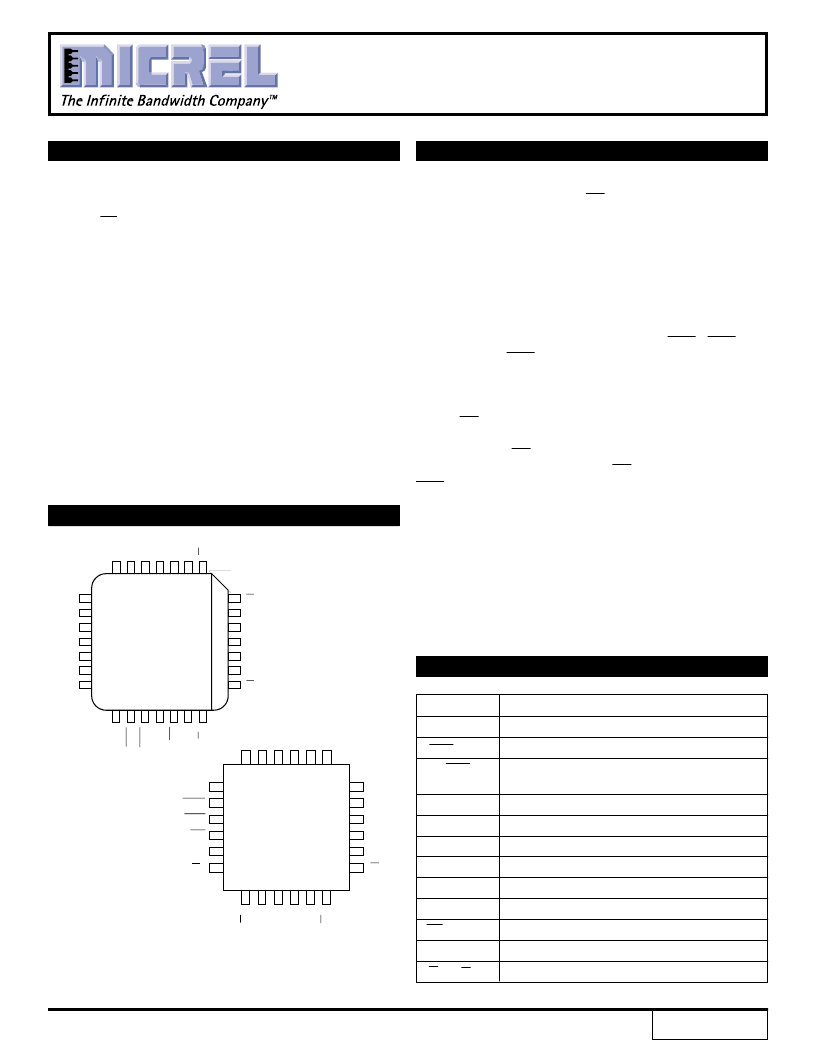

Pin

Function

CP

Clock Pulse Input

CEP

Count Enable Parallel Input (Active LOW)

D

0

/CET

Serial Data Input/Count Enable Trickle

Input (Active LOW)

S

0

— S

2

Select Inputs

MR

Master Reset Input

V

EES

V

EE

Substrate

V

CCA

V

CCO

for ECL Outputs

P

0

– P

3

Preset Inputs

D

3

Serial Data Input

TC

Terminal Count Output

Q

0

— Q

3

Data Outputs

Q

0

— Q

3

Complementary Data Outputs

PIN NAMES

SY100S336A

ENHANCED 4-STAGE

COUNTER/SHIFT REGISTER

I

Max. shift frequency of 700MHz

I

Clock to Q delay max. of 1100ps

I

S

n

to TC speed improved by 50%

I

S

n

set-up and hold time reduced by more than 50%

I

I

EE

min. of –170mA

I

Industry standard 100K ECL levels

I

Internal 75K

input pull-down resistors

I

Extended supply voltage option:

V

EE

= –4.2V to –5.5V

I

Voltage and temperature compensation for improved

noise immunity

I

50% faster than Fairchild 300K at lower power

I

Function and pinout compatible with Fairchild F100K

I

Available in 24-pin CERPACK and 28-pin PLCC

packages

FEATURES

DESCRIPTION

The SY100S336A is functionally the same as the

SY100S336, but has S

n

to TC speed and Sn set-up and

hold times significantly improved, allowing for higher clock

frequency when used as a cascaded multi-stage counter.

The SY100S336A functions either as a modulo-16 up/

down counter or as a 4-bit bidirectional shift register and is

designed for use in high-performance ECL systems. Three

Select inputs (Sn) are provided for determining the mode of

operation. The Function Table lists the available modes of

operation. In order to allow cascading for multistage

counters, two Count Enable controls (CEP, CET) are

provided. The CET input also functions as the Serial Data

input (S

0

) for a shift-up operation, while the D

3

input serves

as the Serial Data input for the shift-down operation.

When the device is in the counting mode, the Terminal

Count (TC) goes to a logical LOW when the count reaches

15 for count-up or reaches 0 for count-down. When in the

shift mode, the TC output simply repeats the Q

3

output.

The flexiblity provided by the TC/Q

3

output and the D

0

/

CET input allows these signals to be interconnected from

one stage to the next higher stage for multistage counting

or shift-up operations. The individual Presets (P

n

) allow

initialization of the counter by entering data in parallel to

preset the counter. A logic HIGH on the Master Reset (MR)

overrides all other inputs and asynchronously clears the

flip-flops. An additional synchronous Clear is provided, as

well as a complement function which synchronously inverts

the contents of the flip-flops. All inputs have 75K

pull-

down resistors.

Q

2

Q

2

V

CCA

V

CC

V

CC

Q

1

Q

1

P

0

CP

V

EE

V

EES

MR

S

0

S

1

4

3

2

1

28

27

26

12

13

14

15

16

17

18

19

11

20

10

21

9

22

8

23

7

24

6

Top View

PLCC

J28-1

25

5

P

1

P

2

P

3

V

E

D

3

Q

3

Q

3

D

0

/

V

E

C

T

S

2

Q

0

Q

0

Rev.: G

Issue Date:

Amendment: /0

July, 1999

S

1

S

0

M

V

E

C

P

0

P

1

P

2

P

3

D

3

Q

3

Q

3

S

2

D

0

/CET

Q

0

Q

0

CEP

TC

18

17

16

15

14

13

1

2

3

4

5

6

7

24

8

23

9

22

10

21

11

20

12

19

Top View

Flatpack

F24-1

V

C

V

C

Q

1

Q

2

Q

1

Q

2

PIN CONFIGURATIONS

1

相關PDF資料 |

PDF描述 |

|---|---|

| SY100S336AJC | ENHANCED 4-STAGE COUNTER/SHIFT REGISTER |

| SY100S336AJCTR | ENHANCED 4-STAGE COUNTER/SHIFT REGISTER |

| SY100S839V | ±2/4, ±4/5/6 CLOCK GENERATION CHIP |

| SY100S839VZC | ±2/4, ±4/5/6 CLOCK GENERATION CHIP |

| SY100S839VZCTR | ±2/4, ±4/5/6 CLOCK GENERATION CHIP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| SY100S336AJC | 功能描述:IC COUNTER/SHIFT REG 28-PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - 專用邏輯 系列:100S 產品變化通告:Product Discontinuation 25/Apr/2012 標準包裝:1,500 系列:74SSTV 邏輯類型:DDR 的寄存緩沖器 電源電壓:2.3 V ~ 2.7 V 位數:14 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:48-TFSOP(0.240",6.10mm 寬) 供應商設備封裝:48-TSSOP 包裝:帶卷 (TR) |

| SY100S336FC | 功能描述:IC COUNTER/SHIFT REG 24-CERPACK RoHS:否 類別:集成電路 (IC) >> 邏輯 - 專用邏輯 系列:100S 產品變化通告:Product Discontinuation 25/Apr/2012 標準包裝:1,500 系列:74SSTV 邏輯類型:DDR 的寄存緩沖器 電源電壓:2.3 V ~ 2.7 V 位數:14 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:48-TFSOP(0.240",6.10mm 寬) 供應商設備封裝:48-TSSOP 包裝:帶卷 (TR) |

| SY100S336JC | 功能描述:IC COUNTER/SHIFT REG 28-PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - 專用邏輯 系列:100S 產品變化通告:Product Discontinuation 25/Apr/2012 標準包裝:1,500 系列:74SSTV 邏輯類型:DDR 的寄存緩沖器 電源電壓:2.3 V ~ 2.7 V 位數:14 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:48-TFSOP(0.240",6.10mm 寬) 供應商設備封裝:48-TSSOP 包裝:帶卷 (TR) |

| SY100S336JC TR | 功能描述:IC COUNTER/SHIFT REG 28-PLCC RoHS:否 類別:集成電路 (IC) >> 邏輯 - 專用邏輯 系列:100S 產品變化通告:Product Discontinuation 25/Apr/2012 標準包裝:1,500 系列:74SSTV 邏輯類型:DDR 的寄存緩沖器 電源電壓:2.3 V ~ 2.7 V 位數:14 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:48-TFSOP(0.240",6.10mm 寬) 供應商設備封裝:48-TSSOP 包裝:帶卷 (TR) |

| SY100S341FC | 功能描述:IC SHIFT REGISTER 8BIT 24CERPACK RoHS:否 類別:集成電路 (IC) >> 邏輯 - 觸發器 系列:100S 標準包裝:25 系列:74LS 功能:設置(預設)和復位 類型:JK 型 輸出類型:差分 元件數:2 每個元件的位元數:1 頻率 - 時鐘:25MHz 延遲時間 - 傳輸:20ns 觸發器類型:負邊沿 輸出電流高,低:400µA, 8mA 電源電壓:4.75 V ~ 5.25 V 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:16-DIP(0.300",7.62mm) 包裝:管件 其它名稱:74LS11274LS112AN74LS112NDM74LS112N |

發布緊急采購,3分鐘左右您將得到回復。