- 您現在的位置:買賣IC網 > PDF目錄98217 > THS10082IDAG4 (TEXAS INSTRUMENTS INC) 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 PDF資料下載

參數資料

| 型號: | THS10082IDAG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| 封裝: | GREEN, PLASTIC, TSSOP-32 |

| 文件頁數: | 8/37頁 |

| 文件大小: | 350K |

| 代理商: | THS10082IDAG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁當前第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

THS10082

SLAS254B MAY 2002 REVISED NOVEMBER 2002

www.ti.com

16

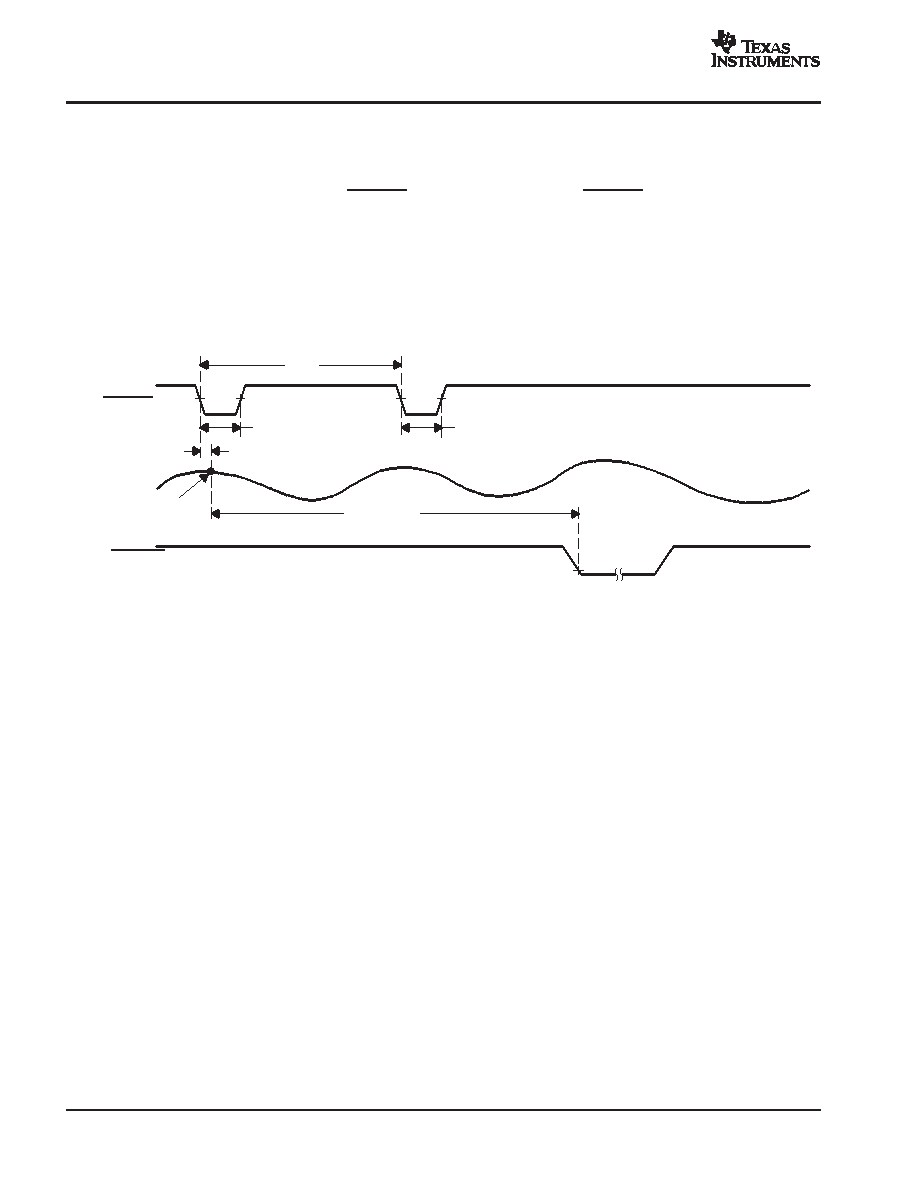

SINGLE CONVERSION MODE

In single conversion mode, a single conversion of the selected analog input channels is performed. The single conversion

mode is selected by setting bit 1 of control register 0 to 1.

A single conversion is initiated by pulsing the CONVST input. On the falling edge of CONVST, the sample and hold stages

of the selected analog inputs are placed into hold simultaneously, and the conversion sequence for the selected channels

is started.

The conversion clock in single conversion mode is generated internally using a clock oscillator circuit. The signal DATA_AV

(data available) becomes active when the trigger level is reached and indicates that the converted sample(s) is (are) written

into the FIFO and can be read out. The trigger level in the single conversion mode can be selected according to Table 13.

Figure 26 shows the timing of the single conversion mode. In this mode, up to two analog input channels can be selected

to be sampled simultaneously (see Table 2).

CONVST

AIN

Sample N

t1

td(A)

t2

tDATA_AV

DATA_AV,

Trigger Level = 1

Figure 26. Timing of Single Conversion Mode

The time (t2) between consecutive starts of single conversions is dependent on the number of selected analog input

channels. The time tDATA_AV, until DATA_AV becomes active is given by: tDATA_AV = tpipe + n × tc. This equation is valid for

a trigger level which is equivalent to the number of selected analog input channels. For all other trigger level conditions refer

to the timing specifications of single conversion mode.

CONTINUOUS CONVERSION MODE

The internal clock oscillator used in the single-conversion mode is switched off in continuous conversion mode. In

continuous conversion mode, (bit 1 of control register 0 set to 0) the ADC operates with a free running external clock signal

CONV_CLK. With every rising edge of the CONV_CLK signal a new converted value is written into the FIFO.

Figure 27 shows the timing of continuous conversion mode when one analog input channel is selected. The maximum

throughput rate is 8 MSPS in this mode. The timing of the DATA_AV signal is shown here in the case of a trigger level set

to 1 or 4.

相關PDF資料 |

PDF描述 |

|---|---|

| THS1009CDAR | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009CDA | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009IDA | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009IDAR | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

| THS1009IDAG4 | 2-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO32 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| THS1009 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDA | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDAG4 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDAR | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

| THS1009CDARG4 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT, 2 ANALOG INPUT, 8 MSPS, SIMULTANEOUS SAMPLING ANALOG-TO-DIGITAL CONVERTER |

發布緊急采購,3分鐘左右您將得到回復。