- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98217 > THS1031CDW (TEXAS INSTRUMENTS INC) 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 PDF資料下載

參數(shù)資料

| 型號(hào): | THS1031CDW |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| 封裝: | GREEN, PLASTIC, SOIC-28 |

| 文件頁(yè)數(shù): | 38/41頁(yè) |

| 文件大小: | 728K |

| 代理商: | THS1031CDW |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)當(dāng)前第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)

THS1031

3-V TO 5.5-V, 10-BIT, 30 MSPS

CMOS ANALOG-TO-DIGITAL CONVERTER

SLAS242E – NOVEMBER 1999 – REVISED MARCH 2002

6

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

electrical characteristics over recommended operating conditions, AVDD = 3 V, DVDD = 3 V,

fs = 30 MSPS/50% duty cycle, MODE = AVDD, 2-V input span from 0.5 V to 2.5 V, external reference,

PGA = 1X, TA = Tmin to Tmax (unless otherwise noted) (continued)

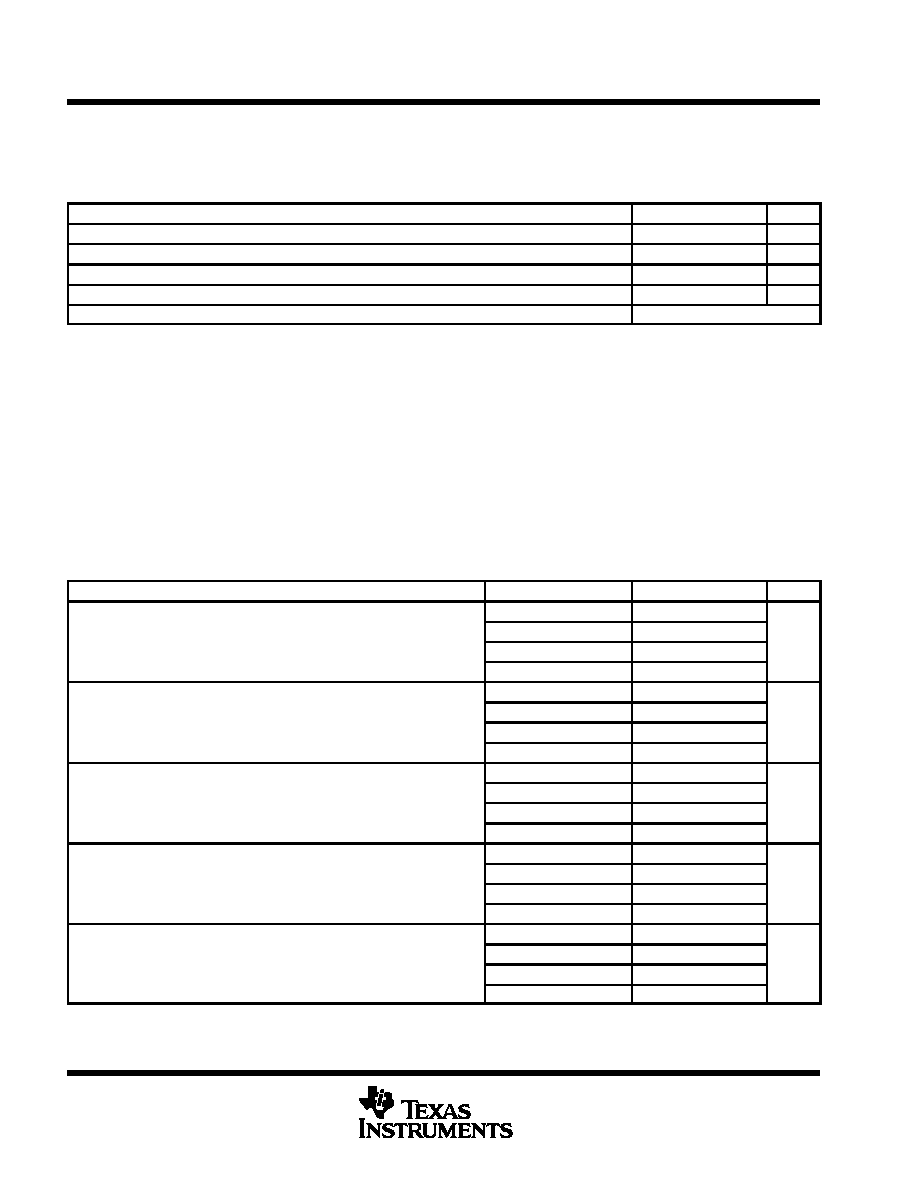

dc accuracy

PARAMETER

MIN

TYP

MAX

UNIT

INL

Integral nonlinearity (see Note 1)

±1

±2

LSB

DNL

Differential nonlinearity (see Note 2)

±0.3

±1

LSB

Offset error (see Note 3)

0.4

2

%FSR

Gain error (see Note 4)

1.4

3.5

%FSR

Missing code

No missing code assured

NOTES:

1. Integral nonlinearity refers to the deviation of each individual code from a line drawn from zero to full scale. The point used as zero

occurs 1/2 LSB before the first code transition. The full-scale point is defined as a level 1/2 LSB beyond the last code transition. The

deviation is measured from the center of each particular code to the true straight line between these two endpoints.

2. An ideal ADC exhibits code transitions that are exactly 1 LSB apart. DNL is the deviation from this ideal value. Therefore this measure

indicates how uniform the transfer function step sizes are. The ideal step size is defined here as the step size for the device under

test (i.e., (last transition level – first transition level)

÷ (2 n – 2)). Using this definition for DNL separates the effects of gain and offset

error. A minimum DNL better than –1 LSB ensures no missing codes.

3. Offset error is defined as the difference in analog input voltage – between the ideal voltage and the actual voltage – that will switch

the ADC output from code 0 to code 1. The ideal voltage level is determined by adding the voltage corresponding to 1/2 LSB to the

bottom reference level. The voltage corresponding to 1 LSB is found from the difference of top and bottom references divided by

the number of ADC output levels (1024).

4. Gain error is defined as the difference in analog input voltage – between the ideal voltage and the actual voltage – that will switch

the ADC output from code 1022 to code 1023. The ideal voltage level is determined by subtracting the voltage corresponding to 1.5

LSB from the top reference level. The voltage corresponding to 1 LSB is found from the difference of top and bottom references

divided by the number of ADC output levels (1024).

dynamic performance (ADC and PGA)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

f = 3.5 MHz

8.2

9

ENOB

Effective number of bits

f = 3.5 MHz, AVDD = 5 V

8.8

Bits

ENOB

Effective number of bits

f = 15 MHz

7.7

Bits

f = 15 MHz, AVDD = 5 V

7.64

f = 3.5 MHz

55

60

SFDR

Spurious free dynamic range

f = 3.5 MHz, AVDD = 5 V

63

dB

SFDR

Spurious free dynamic range

f = 15 MHz

48

dB

f = 15 MHz, AVDD = 5 V

52.4

f = 3.5 MHz

– 58.2

– 54.7

THD

Total harmonic distortion

f = 3.5 MHz, AVDD = 5 V

– 68.7

dB

THD

Total harmonic distortion

f = 15 MHz

– 47

dB

f = 15 MHz, AVDD = 5 V

– 51.9

f = 3.5 MHz

51.2

56

SNR

Signal to noise ratio

f = 3.5 MHz, AVDD = 5 V

55

dB

SNR

Signal-to-noise ratio

f = 15 MHz

53

dB

f = 15 MHz, AVDD = 5 V

49.3

f = 3.5 MHz

51.1

56

SINAD

Signal to noise and distortion

f = 3.5 MHz, AVDD = 5 V

55

dB

SINAD

Signal-to-noise and distortion

f = 15 MHz

48.1

dB

f = 15 MHz, AVDD = 5 V

47.7

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| THS1031IDWR | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| THS1031IDWG4 | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| THS1031CDWG4 | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| THS1031CPWG4 | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

| THS1031CPWR | 1-CH 10-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PDSO28 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| THS1031CDWG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 30 MSPS 1-Ch RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS1031CDWR | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 30 MSPS 1-Ch RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS1031CDWRG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 30 MSPS 1-Ch RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS1031CPW | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10bit 30MSPS ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| THS1031CPWG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 10-Bit 30 MSPS 1-Ch RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。