- 您現在的位置:買賣IC網 > PDF目錄98229 > THS8133ACPHP (TEXAS INSTRUMENTS INC) PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 PDF資料下載

參數資料

| 型號: | THS8133ACPHP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | DAC |

| 英文描述: | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| 封裝: | PLASTIC, HTQFP-48 |

| 文件頁數: | 21/25頁 |

| 文件大小: | 549K |

| 代理商: | THS8133ACPHP |

THS8133, THS8133A, THS8133B

TRIPLE 10BIT, 80 MSPS VIDEO D/A CONVERTER

WITH TRILEVEL SYNC GENERATION

SLVS204C APRIL 1999 REVISED SEPTEMBER 2000

5

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

Table 2. INS3_INT/M2_INT Selection on M2

LAST

EVENT ON

SYNC

SYNC_T

M1

M2

(see Note 2)

DESCRIPTION

H

→L

L or H

X

INS3_INT

Sync insertion active: SYNC low enables sync generation on 1 (INS3_INT=L) or all 3

(INS3_INT=H) DAC outputs. SYNC_T determines the sync polarity.

L

→H

X

M2_INT

Device mode programming active: The DAC outputs reflect the DAC inputs

(BLANK=H) or are forced to the blanking level (BLANK=L). M2 is interpreted according

to Table 1.

X = don’t care

NOTE 2: M1 and M2 start configuring the device as soon as they are interpreted, which is continuously for M1 (static pin) or on the second rising

edge on CLK after a transition on SYNC for M2. M2 is interpreted as either INS3_INT or M2_INT, as shown in Table 2.

programming example

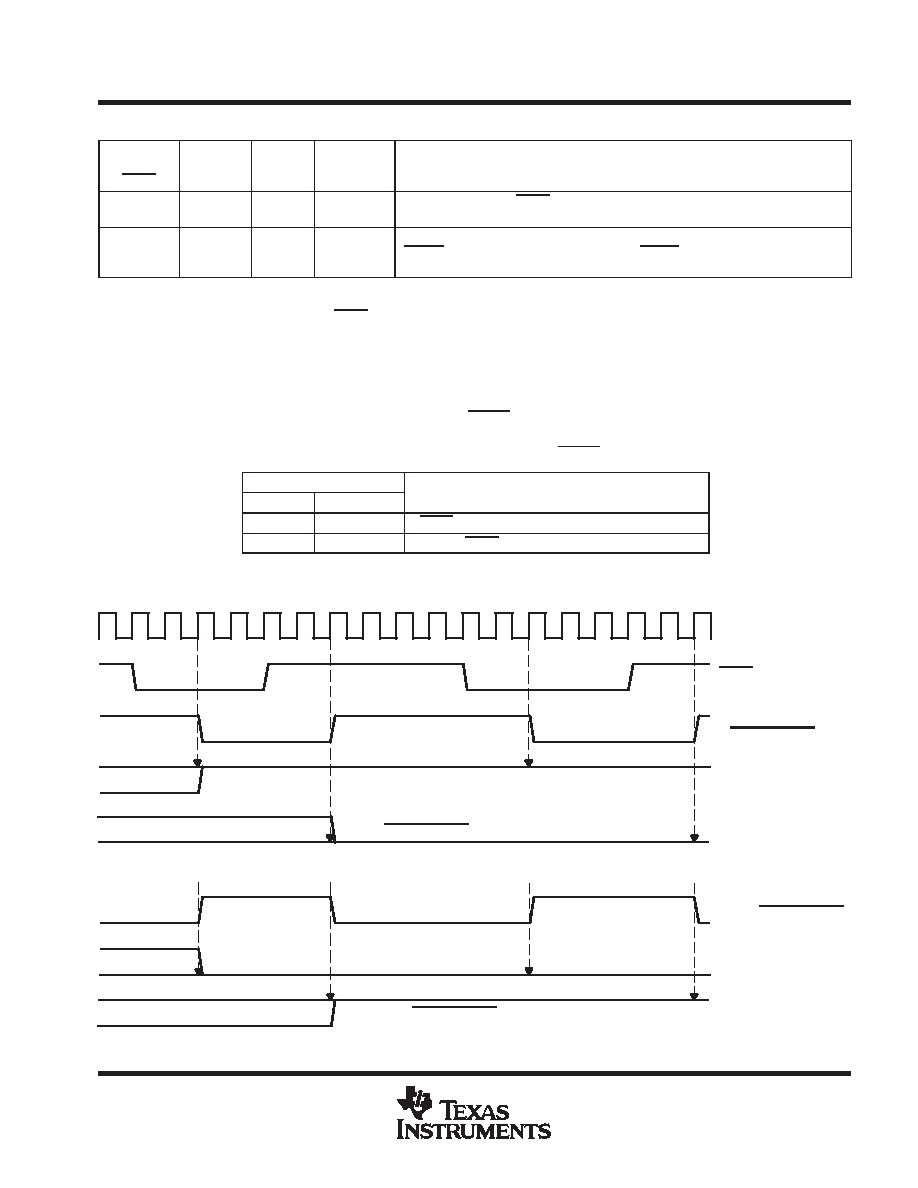

Configuration of the device will normally be static in a given application. If M2_INT and INS3_INT need to be

both low or high, the M2 pin is simply tied low or high. If M2_INT and INS3_INT need to have different levels,

these can be easily derived from the signal on the SYNC pin, as shown in Table 3 and Figure 2.

Table 3. Generating M2 From SYNC

In order to have:

Apply to M2:

M2_INT

INS3_INT

Apply to M2:

L

H

...SYNC delayed by 2 CLK periods

H

L

...inverted SYNC delayed by 2 CLK periods

The input formats and latencies are shown in Figures 35 for each operation mode.

CLK

SYNC

M2

[=SYNC_delayed]

INS3_INT

M2_INT

M2

[=NOT SYNC_delayed]

INS3_INT

M2_INT

if (M2 = SYNC_delayed)

M2_INT = L and INS3_INT = H)

if (M2 = NOT SYNC_delayed)

M2_INT = H and INS3_INT = L)

Figure 2. Generating INS3_INT and M2_INT from M2

相關PDF資料 |

PDF描述 |

|---|---|

| THS8133BCPHP | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8133BCPHPG4 | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8133CPHP | PARALLEL, WORD INPUT LOADING, 0.005 us SETTLING TIME, 10-BIT DAC, PQFP48 |

| THS8134BCPHP | PARALLEL, 8 BITS INPUT LOADING, 0.005 us SETTLING TIME, 8-BIT DAC, PQFP48 |

| THS8134CPHP | PARALLEL, 8 BITS INPUT LOADING, 0.005 us SETTLING TIME, 8-BIT DAC, PQFP48 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| THS8133ATQFP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 10-BIT, 80 MSPS VIDEO D/A CONVERTER WITH TRI-LEVEL SYNC GENERATION |

| THS8133B | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 10-BIT, 80 MSPS VIDEO D/A CONVERTER WITH TRI-LEVEL SYNC GENERATION WITH TRI-LEVEL SYNC GENERATION |

| THS8133BCPGP | 制造商:Texas Instruments 功能描述: |

| THS8133BCPHP | 功能描述:數字化視頻/模擬轉換器集成電路 10B 80 MSPS Triple Video DAC RoHS:否 制造商:Texas Instruments 轉換器數量:3 輸出類型:Current 轉換速率:180 MSPs 分辨率:10 bit 接口類型:Parallel 電壓參考:Internal or External 積分非線性:- 2.5 LSB, 1.5 LSB 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:HTQFP 封裝:Tray |

| THS8133BCPHPG4 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 10-BIT, 80 MSPS VIDEO D/A CONVERTER WITH TRI-LEVEL SYNC GENERATION WITH TRI-LEVEL SYNC GENERATION |

發布緊急采購,3分鐘左右您將得到回復。