- 您現在的位置:買賣IC網 > PDF目錄98229 > THS8134CPHP (TEXAS INSTRUMENTS INC) PARALLEL, 8 BITS INPUT LOADING, 0.005 us SETTLING TIME, 8-BIT DAC, PQFP48 PDF資料下載

參數資料

| 型號: | THS8134CPHP |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | DAC |

| 英文描述: | PARALLEL, 8 BITS INPUT LOADING, 0.005 us SETTLING TIME, 8-BIT DAC, PQFP48 |

| 封裝: | PLASTIC, HTQFP-48 |

| 文件頁數: | 21/27頁 |

| 文件大小: | 553K |

| 代理商: | THS8134CPHP |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁當前第21頁第22頁第23頁第24頁第25頁第26頁第27頁

THS8134, THS8134A, THS8134B

TRIPLE 8BIT, 80 MSPS VIDEO D/A CONVERTER

WITH TRILEVEL SYNC GENERATION

SLVS205D MAY 1999 REVISED MARCH 2000

3

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

Terminal Functions (Continued)

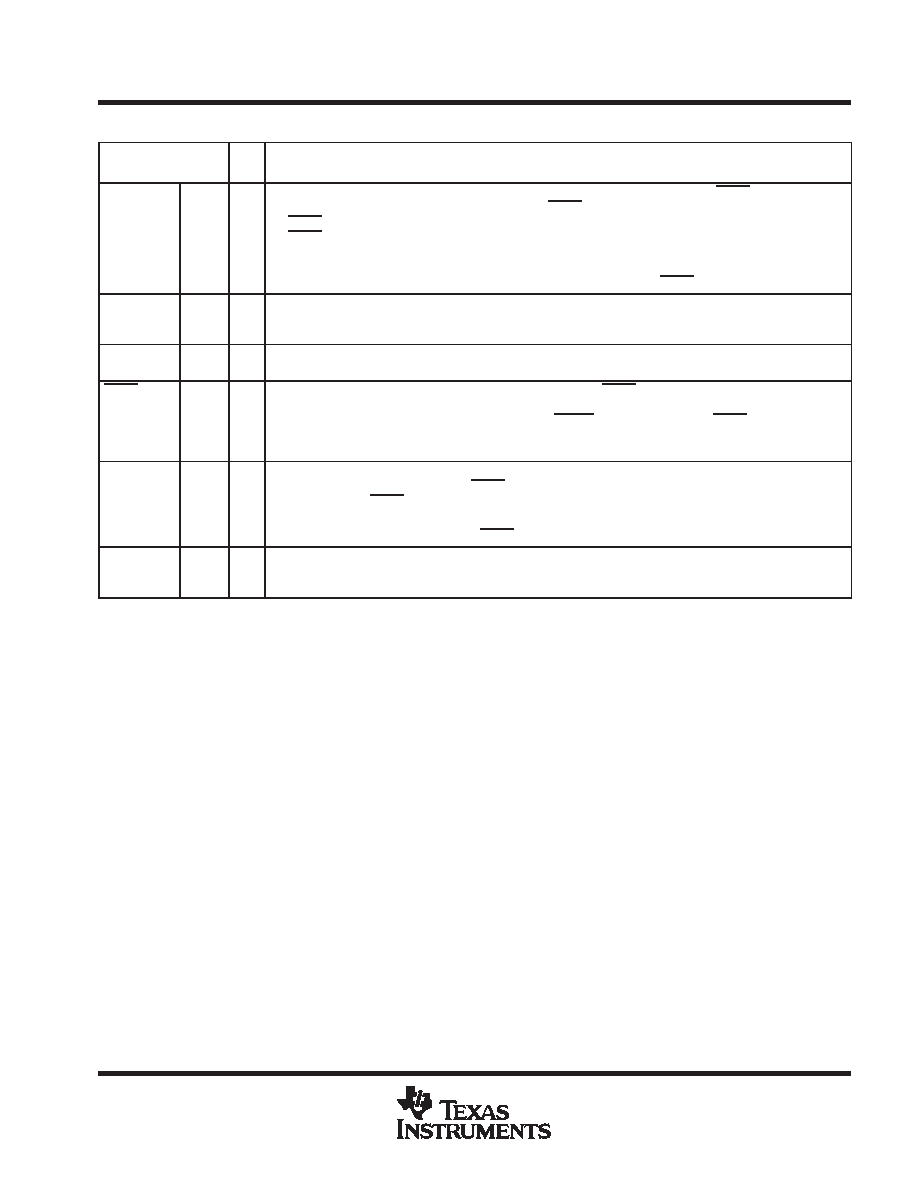

TERMINAL

I/O

DESCRIPTION

NAME

PIN

I/O

DESCRIPTION

M2

48

I

Operation mode control 2. The second rising edge on CLK after a transition on SYNC latches M2. The

interpretation is dependent on the polarity of the last SYNC transition:

SYNC L to H: latched as M2_INT

SYNC H to L: latched as INS3_INT

Together with M1, M2_INT configures the device as shown in Table 1. When INS3_INT is high, the sync output is

inserted on all DAC outputs; a low will insert it only on the AGY output. See also Figure 2 and Table 2. The value of

M2 at power-up is undetermined. Therefore at least 1 L

→ H transition on SYNC is required to set M2.

NC

9, 10,

13, 14,

35, 36

Not connected

RPr0RPr7

1522

I

Red or Pr pixel data input bus. Index 0 denotes the least significant bit. Refer to functional description for different

operating modes.

SYNC

24

I

Sync control input, active low. A rising edge on CLK latches SYNC. When asserted, only the AGY output

(INS3_INT=L, see terminal M2) or ARPr, AGY and ABPb outputs (INS3_INT=H, see terminal M2) are driven to

the sync level, irrespective of the values on the data or BLANK inputs. Consequently, SYNC should remain low

for the whole duration of sync, which is in the case of a tri-level sync both the negative and positive portion (see

Figure 7).

SYNC_T

25

I

Sync tri-level control, active high. A rising edge on CLK latches SYNC_T. When asserted, a positive sync (higher

than blanking level) is generated when SYNC is low. When disabled, a negative sync (lower than blanking level)

is generated when SYNC is low. When generating a tri-level (negative-to-positive) sync, a L

→ H transition on

this signal positions the start of the positive transition. See Figure 6 for timing control.

The value on SYNC_T is ignored when SYNC is not asserted (high).

VREF

37

I/O

Voltage reference for DACs. An internal voltage reference of nominally 1.35 V is provided, which requires an

external 0.1

F ceramic capacitor between VREF and AVSS. However, the internal reference can be overdriven

by an externally supplied reference voltage.

相關PDF資料 |

PDF描述 |

|---|---|

| THS8134ACPHP | PARALLEL, 8 BITS INPUT LOADING, 0.005 us SETTLING TIME, 8-BIT DAC, PQFP48 |

| THS8135-240IPHP | PARALLEL, WORD INPUT LOADING, 10-BIT DAC, PQFP48 |

| THS8135-80CPHP | PARALLEL, WORD INPUT LOADING, 10-BIT DAC, PQFP48 |

| THS8135-80IPHP | PARALLEL, WORD INPUT LOADING, 10-BIT DAC, PQFP48 |

| THS8135-240CPHP | PARALLEL, WORD INPUT LOADING, 10-BIT DAC, PQFP48 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| THS8134TQFP | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 8-BIT, 80 MSPS VIDEO D/A CONVERTER WITH TRI-LEVEL SYNC GENERATION |

| THS8135 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 10-BIT, 240 MSPS VIDEO DAC WITH TRI-LEVEL SYNC AND VIDEO (ITU-R.BT601) COMPLIANT FULL SCALE RANGE |

| THS8135EVM | 功能描述:視頻 IC 開發工具 Triple 10B 240MSPS RoHS:否 制造商:Texas Instruments 產品:Evaluation Boards 類型:YPbPr to RGBHV Converters 工具用于評估:LMH1251 工作電源電壓:5 V |

| THS8135PHP | 功能描述:數字化視頻/模擬轉換器集成電路 Triple 10B 240MSPS Video DAC RoHS:否 制造商:Texas Instruments 轉換器數量:3 輸出類型:Current 轉換速率:180 MSPs 分辨率:10 bit 接口類型:Parallel 電壓參考:Internal or External 積分非線性:- 2.5 LSB, 1.5 LSB 電源電壓-最大:3.6 V 電源電壓-最小:3 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:HTQFP 封裝:Tray |

| THS8135PHP | 制造商:Texas Instruments 功能描述:10BIT DAC 240MSPS TRIPLE SMD |

發布緊急采購,3分鐘左右您將得到回復。