- 您現在的位置:買賣IC網 > PDF目錄98239 > TLC4545ID (TEXAS INSTRUMENTS INC) 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 PDF資料下載

參數資料

| 型號: | TLC4545ID |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| 封裝: | GREEN, PLASTIC, MS-012AA, SOIC-8 |

| 文件頁數: | 23/26頁 |

| 文件大小: | 652K |

| 代理商: | TLC4545ID |

TLC4541, TLC4545

SLAS293 DECEMBER 2001

6

www.ti.com

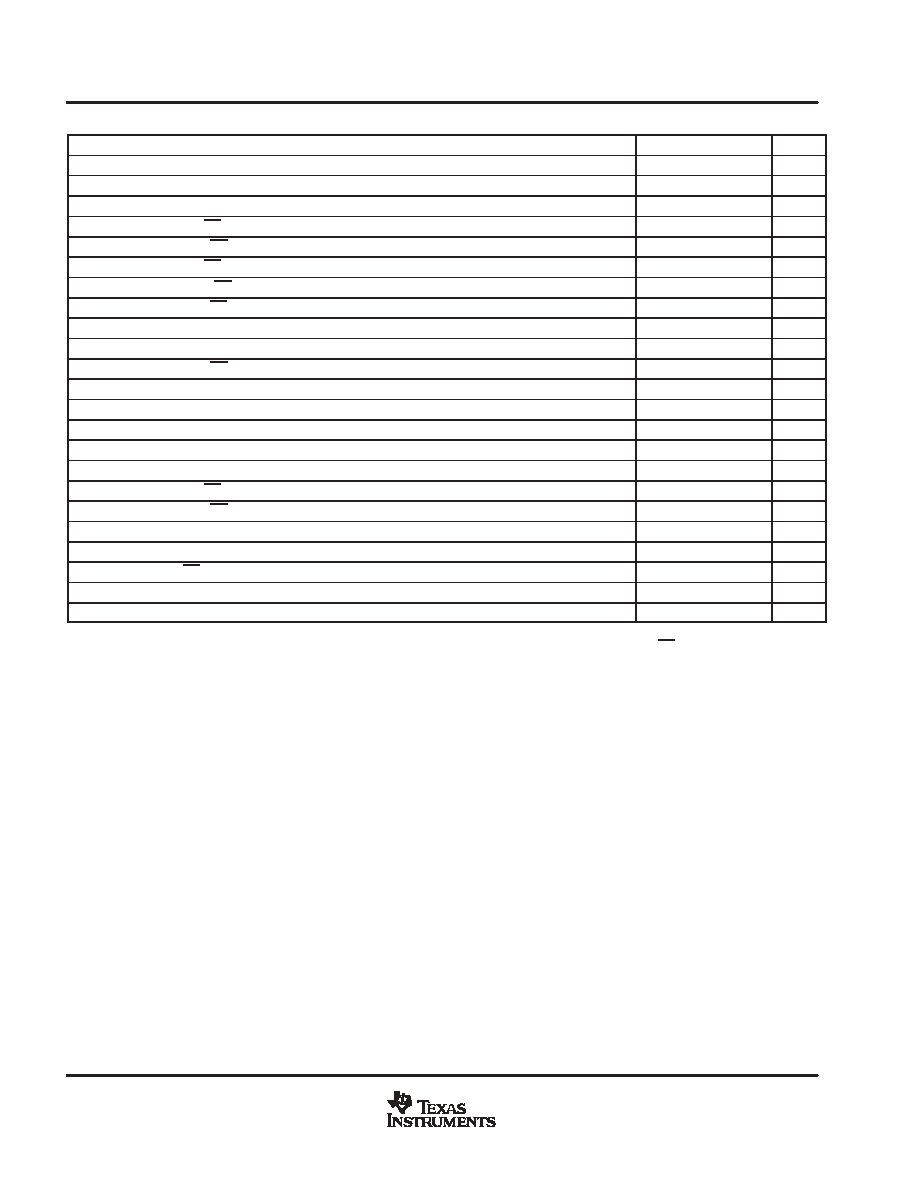

timing requirements, VDD = 5 V, VREF = 4.096 V, SCLK frequency = 15 MHz (unless otherwise specified)

MIN

TYP

MAX

UNIT

tcyc(SCLK) SCLK cycle time, VDD = 4.5 V to 5.5 V (see Note 3)

66

10000

ns

tw1

Pulse width, SCLK low

27

5000

ns

tw2

Pulse width, SCLK high

27

5000

ns

th1

Hold time, CS high after SCLK falling edge

3

ns

tsu1

Setup time, CS falling edge before the first SCLK falling edge

15

ns

th2

Hold time, CS low after 16th SCLK falling edge

5

ns

tw3

Pulse width, CS high

0.5

SCLKs

td1

Delay time, CS falling edge to SDO MSB valid, VDD = VREF = 4.5 V, 20 pF

12

17

ns

td2

Delay time, SCLK rising edge to next SDO data bit valid, VDD = VREF = 4.5 V, 20 pF

15

ns

td3

Delay time, 17th SCLK rising edge to SDO 3-stated, VDD = VREF = 4.5 V, 20 pF (see Note 4)

20

ns

tsu3

Setup time, CS falling edge before FS rising edge (TLC4541 only)

0.5

1

SCLKs

tw4

Pulse width, FS high (TLC4541 only)

0.5

1

SCLKs

tsu4

Setup time, FS rising edge before SCLK falling edge (TLC4541 only)

12.5

ns

th4

Hold time, FS high after SCLK falling edge (TLC4541 only)

5

ns

tsu5

Setup time, FS falling edge before 1st SCLK falling edge (TLC4541 only)

12

ns

td4

Delay time, FS rising edge to SDO MSB valid, (VDD = VREF = 4.5 V, 20 pF TLC4541 only)

15

ns

th6

Hold time, CS low after 1st SCLK falling edge

5

ns

tsu6

Setup time, CS rising edge before 9th (or the last) SCLK falling edge

5

ns

th7

Hold time, FS low after 1st SCLK falling edge (TLC4541 only)

5

ns

tsu7

Setup time, FS rising edge before 9th (or the last) SCLK falling edge

5

ns

tcyc(reset)

Active CS/FS cycle time, SCLK falling edges required to initialize ADC

1

8

SCLKs

tconv

Conversion time (22 conversion clocks based on 7.5-MHz to 12-MHz OSC)

1.83

2.94

s

ts

Sample time, 20 SCLKs, SCLK up to 15 MHz

1.33

200

s

NOTES:

3. Timing specifications given for 40/60 to 60/40 duty cycle

4. SDO goes into the high impedance state after detection of the 17th rising SCLK edge or a rising CS edge if a 17th SCLK is not

presented.

相關PDF資料 |

PDF描述 |

|---|---|

| TLC4545IDG4 | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLC4545IDGKG4 | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLC4545IDR | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLC4541IDGKG4 | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLC4541ID | 1-CH 16-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLC4545ID | 制造商:Texas Instruments 功能描述:IC 16BIT ADC SMD 4545 SOIC8 |

| TLC4545IDG4 | 功能描述:模數轉換器 - ADC 16-Bit 200KSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLC4545IDGK | 功能描述:模數轉換器 - ADC 16-Bit 200KSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLC4545IDGKG4 | 功能描述:模數轉換器 - ADC 16-Bit 200KSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLC4545IDGKR | 功能描述:模數轉換器 - ADC 16-Bit 200KSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發布緊急采購,3分鐘左右您將得到回復。