- 您現在的位置:買賣IC網 > PDF目錄98249 > TLV1572CDRG4 (TEXAS INSTRUMENTS INC) 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 PDF資料下載

參數資料

| 型號: | TLV1572CDRG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| 封裝: | GREEN, PLASTIC, SOIC-8 |

| 文件頁數: | 3/15頁 |

| 文件大小: | 348K |

| 代理商: | TLV1572CDRG4 |

TLV1572

2.7 V TO 5.5 V, 10-BIT, 1.25 MSPS

SERIAL ANALOG-TO-DIGITAL CONVERTER WITH AUTO-POWERDOWN

SLAS171A – DECEMBER 1997– REVISED SEPTEMBER 1998

11

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

APPLICATION INFORMATION

interfacing TLV1572 to SPI/QSPI compatible microcontrollers(

Cs) (continued)

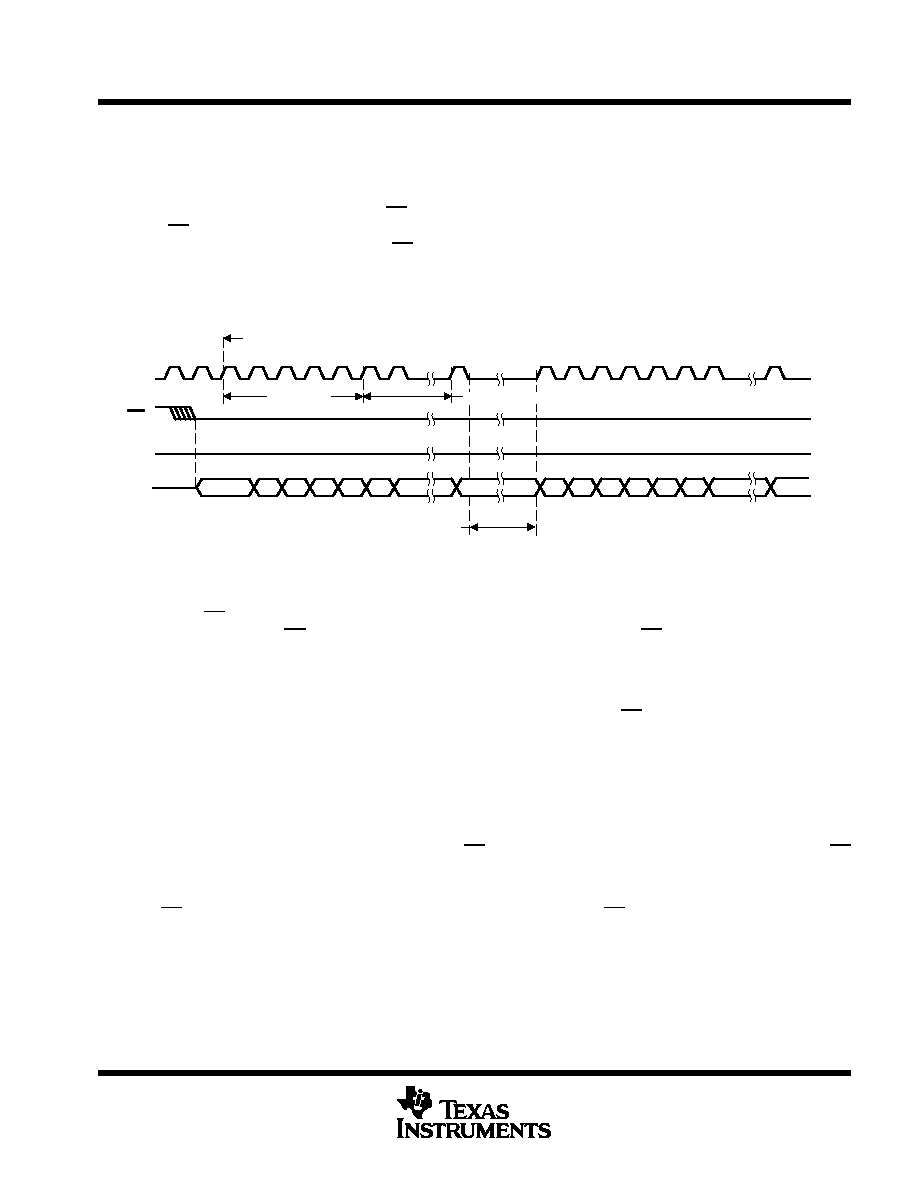

Unlike the DSP mode in which the conversion is initiated by the FS input signal from the DSP, the conversion

is initiated by the incoming SCLK after CS falls. Sampling of the input is started on the first rising edge of SCLK

after CS goes low. After six null bits, the A/D conversion data becomes available on SCLK rising edges and is

latched by the

C on the falling edges. CS can be pulled high during the conversion before the LSB is shifted

out to use the device as a lower resolution ADC. Figure 9 shows the

C mode timing diagram.

The device goes into autopower down after the LSB is shifted out and is brought out of powerdown by the next

clock rising edge as shown in Figure 9.

12

3

4

5

6

7

16

0

LSB (N)

SCLK

CS

FS

DO

MSB

12

3

4

5

6

7

16

0

Autopower Down

0

LSB(N+1)

Sampling

Conversion

Sample (N)

(N)

MSB(N+1)

Figure 9.

C Application Timing Diagram

key points

1.

When CS goes low, if FS is high, it is in

C ({Q}SPI) mode. Thus, FS is tied to VDD. FS is latched twice, on

the falling edge of CS and again on an internally delayed falling edge of CS. Only if both latches latch 1,

then

C mode is set else DSP mode is set. Only polarity = 0 is supported, i.e. SCLK idles low. Only

clock_phase = 1 is supported as shown in the timing diagrams.

2.

For each conversion 16 clocks have to be supplied. If the

C cannot take in 16 bits at a time, it may take

8 bits with 8 clocks and the next 8 bits with another 8 clocks keeping CS low throughout the conversion.

The delay between these two 8-clock periods must not be longer than 100

s.

3.

Sampling starts on the first rising edge of SCLK and ends on the edge when the 6th 0 bit is sent out.

Decisions are made on the rising edge and data is output on the same edge but a bit delayed to avoid noise.

4.

The device goes into autopower down on the falling edge of the 16th clock and is brought out of powerdown

by next first (17th) clock rising edge.

5.

If the (Q)SPI wants less than a 16-bit transfer, CS must go high after each transfer. The falling edge of CS

resets the TLV1572 for the next conversion. Thus a 14-bit transfer is possible when using the device as an

8-bit A/D.

6.

CS going high puts the device in 3-state and complete powerdown. CS going low sets the mode and pulls

DO out of 3-state.

相關PDF資料 |

PDF描述 |

|---|---|

| TLV1572ID | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV1572CDG4 | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV1572IDR | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV1572IDRG4 | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV1572IDG4 | 1-CH 10-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLV1572EVM | 功能描述:EVALUATION MODULE FOR TLV1572 RoHS:是 類別:編程器,開發系統 >> 評估板 - 模數轉換器 (ADC) 系列:- 產品培訓模塊:Obsolescence Mitigation Program 標準包裝:1 系列:- ADC 的數量:1 位數:12 采樣率(每秒):94.4k 數據接口:USB 輸入范圍:±VREF/2 在以下條件下的電源(標準):- 工作溫度:-40°C ~ 85°C 已用 IC / 零件:MAX11645 已供物品:板,軟件 |

| TLV1572ID | 功能描述:模數轉換器 - ADC 10bit A/D RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV1572IDG4 | 功能描述:模數轉換器 - ADC 10-Bit 1.25 MSPS 1-Ch DSP RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV1572IDR | 功能描述:模數轉換器 - ADC 10-Bit 1.25 MSPS 1-Ch DSP RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV1572IDRG4 | 功能描述:模數轉換器 - ADC 10-Bit 1.25 MSPS 1-Ch DSP RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發布緊急采購,3分鐘左右您將得到回復。