- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98250 > TLV2542IDG4 (TEXAS INSTRUMENTS INC) 2-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 PDF資料下載

參數(shù)資料

| 型號: | TLV2542IDG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 2-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| 封裝: | GREEN, PLASTIC, SOIC-8 |

| 文件頁數(shù): | 31/31頁 |

| 文件大小: | 778K |

| 代理商: | TLV2542IDG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁當前第31頁

TLV2541, TLV2542, TLV2545

2.7-V TO 5.5-V, LOW-POWER, 12-BIT, 140/200 KSPS,

SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH AUTOPOWER DOWN

SLAS245E MARCH 2000 REVISED APRIL 2010

9

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

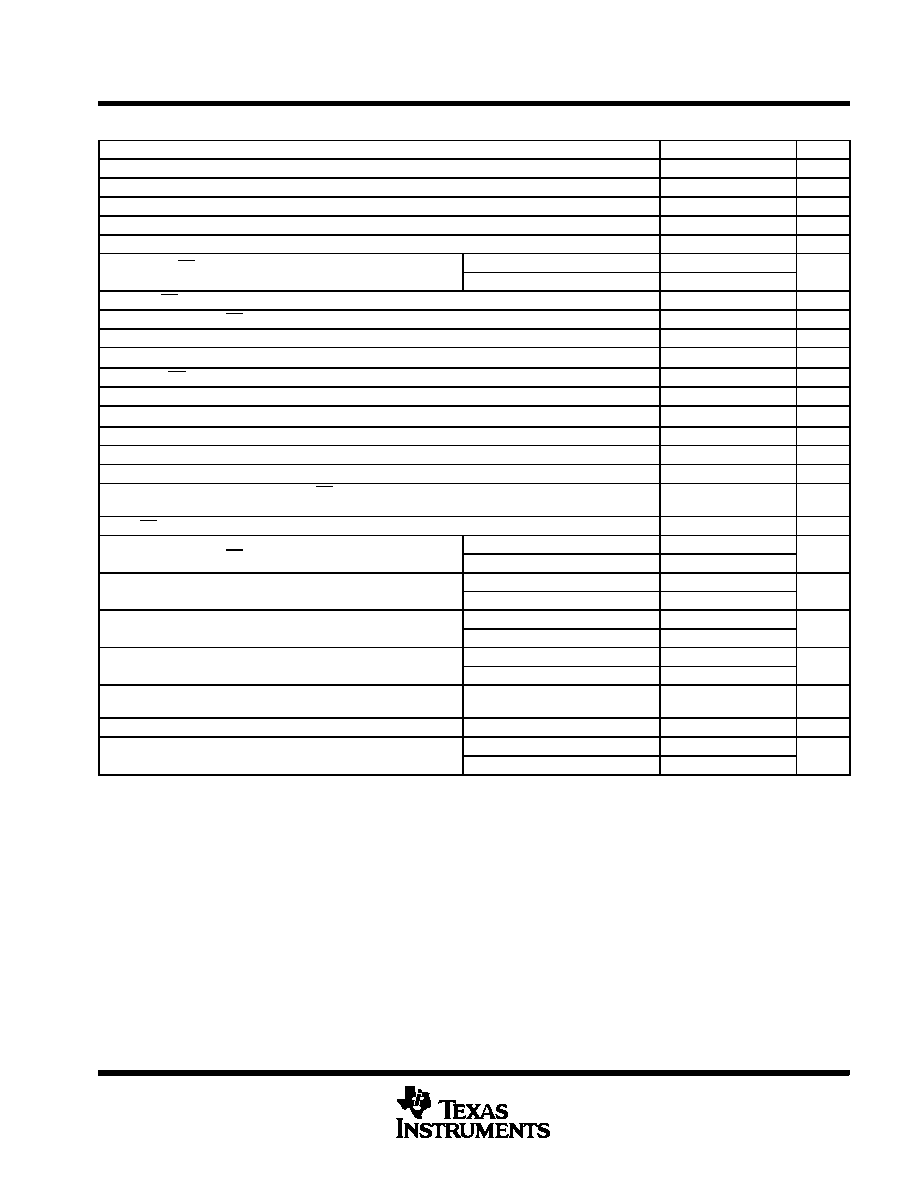

recommended operating conditions

MIN

NOM

MAX

UNIT

Supply voltage, VDD

2.7

3.3

5.5

V

Positive external reference voltage input, VREFP (see Note 1)

2

VDD

V

Analog input voltage (see Note 1)

0

VDD

V

High level control input voltage, VIH

2.1

V

Low-level control input voltage, VIL

0.6

V

Setup time, CS falling edge before first SCLK falling edge, VDD = REF = 4.5 V

40

ns

Setup time, CS falling edge before first SCLK falling edge,

tsu(CSL-SCLKL)

VDD = REF = 2.7 V

70

ns

Hold time, CS falling edge after SCLK falling edge, th(SCLKL-CSL)

5

ns

Delay time, delay from CS falling edge to FS rising edge, td(CSL-FSH) (TLV2541 only)

0.5

7

SCLKs

Setup time, FS rising edge before SCLK falling edge, tsu(FSH-SCLKL) (TLV2541 only)

0.35

SCLKs

Hold time, FS high after SCLK falling edge, th(SCLKL-FSL) (TLV2541 only)

0.65

SCLKs

Pulse width CS high time, tw(H_CS)

100

ns

Pulse width FS high time, tw(H_FS) (TLV2541 only)

0.75

SCLKs

SCLK cycle time, VDD = 3.6 V to 2.7 V, tc(SCLK) (maximum tolerance of 40/60 duty cycle)

90

10000

ns

SCLK cycle time, VDD = 5.5 V to 4.5 V, tc(SCLK) (maximum tolerance of 40/60 duty cycle)

50

10000

ns

Pulse width low time, tw(L_SCLK)

0.4

0.6

SCLK

Pulse width high time, tw(H_SCLK)

0.4

0.6

SCLK

Hold time, hold from end of conversion to CS high, th(EOC-CSH) (EOC is internal, indicates end of conversion

time, tc)

0.05

μs

Active CS cycle time to reset internal MUX to AIN0, t(reset cycle) (TLV2542 only)

4

7

SCLKs

Delay time delay from CS falling edge to SDO valid t

VDD = REF = 4.5 V, 25-pF load

40

ns

Delay time, delay from CS falling edge to SDO valid, td(CSL-SDOV)

VDD = REF = 2.7 V, 25-pF load

70

ns

Delay time, delay from FS falling edge to SDO valid, td(FSL-SDOV) VDD = REF = 4.5 V, 25-pF load

1

ns

Delay time, delay from FS falling edge to SDO valid, td(FSL-SDOV)

(TLV2541 only)

VDD = REF = 2.7 V, 25-pF load

1

ns

Delay time, delay from SCLK rising edge to SDO valid,

VDD = REF = 4.5 V, 25-pF load

11

ns

Delay time, delay from SCLK rising edge to SDO valid,

td(SCLKH-SDOV)

VDD = REF = 2.7 V, 25-pF load

21

ns

Delay time, delay from 17th SCLK rising edge to SDO 3-state,

VDD = REF = 4.5 V, 25-pF load

30

ns

Delay time, delay from 17th SCLK rising edge to SDO 3 state,

td(SCLK17H-SDOZ)

VDD = REF = 2.7 V, 25-pF load

60

ns

Conversion time, tc

Conversion clock = internal

oscillator

2.1

2.6

3.5

μs

Sampling time, t(sample)

See Note 2

300

ns

Operating free air temperature T

TLV2541/2/5C

0

70

°C

Operating free-air temperature, TA

TLV2541/2/5I

40

85

°C

NOTES: 1. Analog input voltages greater than that applied to VREF convert as all ones (111111111111), while input voltages less than that applied

to GND convert as all zeros(000000000000).

2. Minimal t(sample) is given by 0.9 × 50 pF × (RS + 0.5 kΩ), where RS is the source output impedance.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV2545CDGKR | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV2545IDGKG4 | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV2541ID | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV2541IDRG4 | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV2541CDGKRG4 | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV2542IDGK | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12bit SAR ADC RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2542IDGKG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12-Bit 200 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2542IDGKR | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12-Bit 200 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2542IDGKRG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12-Bit 200 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2542IDR | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 12-Bit 200 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發(fā)布緊急采購,3分鐘左右您將得到回復。