- 您現在的位置:買賣IC網 > PDF目錄98250 > TLV2542IDGKR (TEXAS INSTRUMENTS INC) 2-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 PDF資料下載

參數資料

| 型號: | TLV2542IDGKR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 2-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| 封裝: | GREEN, PLASTIC, MSOP-8 |

| 文件頁數: | 26/31頁 |

| 文件大小: | 778K |

| 代理商: | TLV2542IDGKR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁當前第26頁第27頁第28頁第29頁第30頁第31頁

TLV2541, TLV2542, TLV2545

2.7-V TO 5.5-V, LOW-POWER, 12-BIT, 140/200 KSPS,

SERIAL ANALOG-TO-DIGITAL CONVERTERS WITH AUTOPOWER DOWN

SLAS245E MARCH 2000 REVISED APRIL 2010

4

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

POST OFFICE BOX 1443

HOUSTON, TEXAS 772511443

detailed description (continued)

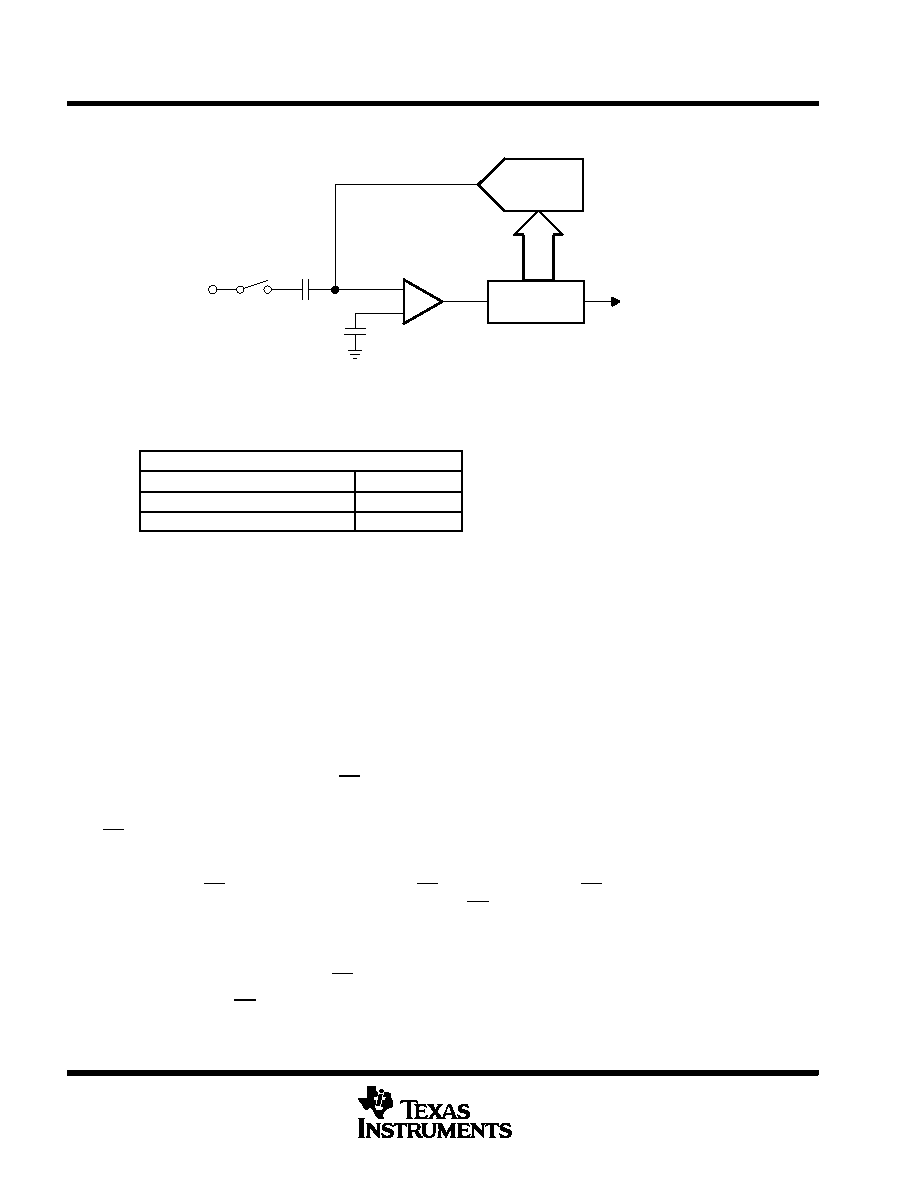

GND/AIN()

ADC Code

AIN

Charge

Redistribution

DAC

Control

Logic

_

+

Figure 1. Simplified SAR Circuit

serial interface

OUTPUT DATA FORMAT

MSB

LSB

D15D4

D3D0

Conversion result (OD11OD0)

Don’t care

The output data format is binary (unipolar straight binary).

binary

Zero-scale code = 000h, Vcode = GND

Full-scale code = FFFh, Vcode = VREF 1 LSB

pseudo-differential inputs

The TLV2545 operates in pseudo-differential mode. The inverted input is available on pin 5. It can have a

maximum input ripple of ±0.2 V. This is normally used for ground noise rejection.

control and timing

start of the cycle

Each cycle may be started by either CS, FS, or a combination of both. The internal state machine requires one

SCLK high-to-low transition to determine the state of these control signals so internal blocks can be powered

up in an active cycle. Special care to SPI mode is necessary. Make sure there is at least one SCLK whenever

CS (pin 1) is high to ensure proper operation.

TLV2541

D Control via CS ( FS = 1 at the falling edge of CS)—The falling edge of CS is the start of the cycle. The MSB

should be read on the first falling SCLK edge after CS is low. Output data changes on the rising edge of

SCLK. This is typically used for a microcontroller with an SPI interface, although it can also be used for a

DSP. The microcontroller SPI interface should be programmed for CPOL = 0 (serial clock referenced to

ground) and CPHA = 1 (data is valid on the falling edge of the serial clock). At least one falling edge transition

on SCLK is needed whenever CS is brought high.

D Control via FS (CS is tied/held low)—The MSB is presented after the rising edge of FS. The falling edge

of FS is the start of the cycle. The MSB should be read on the first falling edge of SCLK after FS is low. This

is the typical configuration when the ADC is the only device on the DSP serial port.

相關PDF資料 |

PDF描述 |

|---|---|

| TLV2542CDGKRG4 | 2-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV2541CDGK | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV2542IDR | 2-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV2545IDR | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

| TLV2542IDG4 | 2-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO8 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLV2542IDGKRG4 | 功能描述:模數轉換器 - ADC 12-Bit 200 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2542IDR | 功能描述:模數轉換器 - ADC 12-Bit 200 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2542IDRG4 | 功能描述:模數轉換器 - ADC 12-Bit 200 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV25431DW | 制造商:Texas Instruments 功能描述: |

| TLV2543C | 制造商:Texas Instruments 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。