- 您現在的位置:買賣IC網 > PDF目錄98251 > TLV2548CDWG4 (TEXAS INSTRUMENTS INC) 8-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 PDF資料下載

參數資料

| 型號: | TLV2548CDWG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 8-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| 封裝: | GREEN, PLASTIC, SOIC-20 |

| 文件頁數: | 23/46頁 |

| 文件大小: | 1078K |

| 代理商: | TLV2548CDWG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁

TLV2544, TLV2548

2.7V TO 5.5V, 12BIT, 200KSPS, 4/8CHANNEL, LOW POWER

SERIAL ANALOGTODIGITAL CONVERTERS WITH AUTOPOWERDOWN

SLAS198E FEBRUARY 1999 REVISED JUNE 2003

3

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

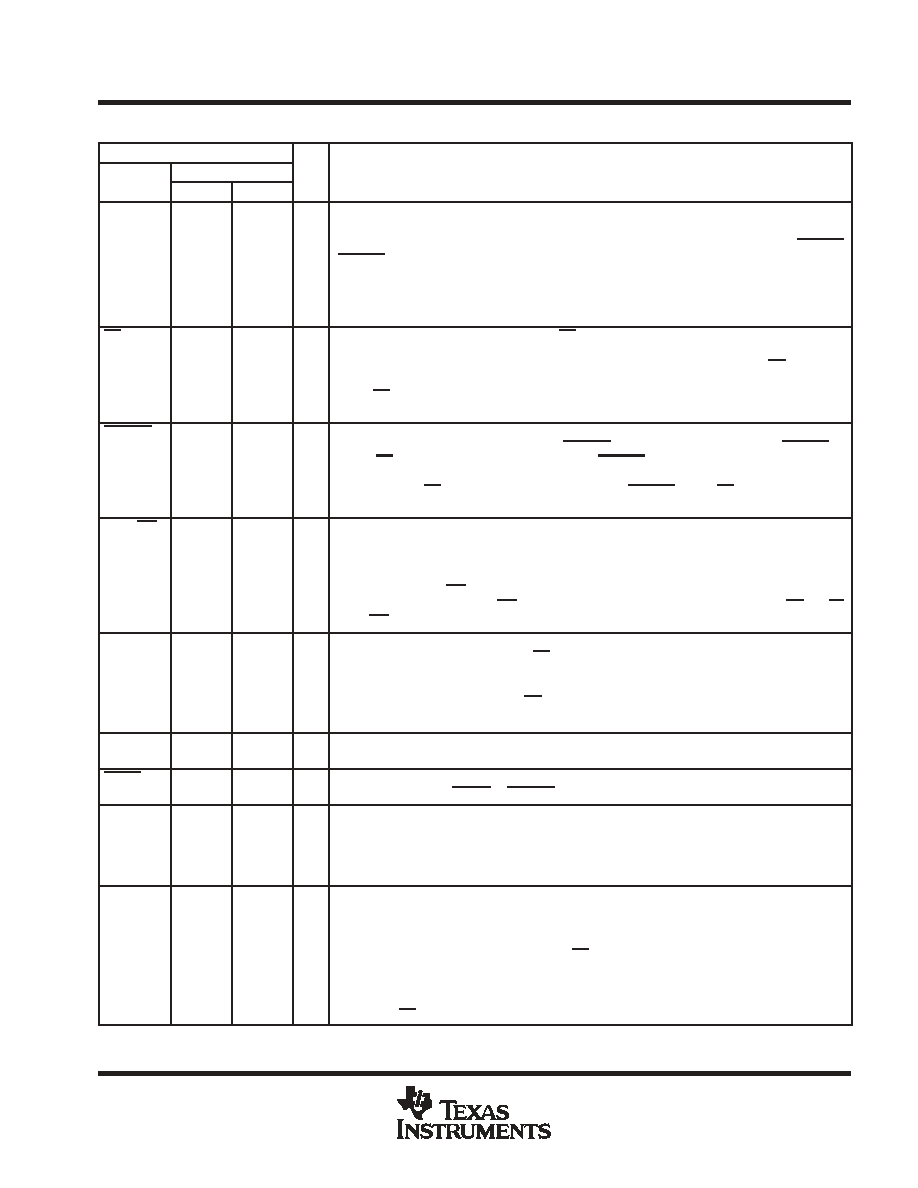

Terminal Functions

TERMINAL

NAME

NO.

I/O

DESCRIPTION

NAME

TLV2544

TLV2548

I/O

DESCRIPTION

A0

A1

A2

A3

A0

A1

A2

A3

A4

A5

A6

A7

6

7

8

9

6

7

8

9

10

11

12

13

I

Analog signal inputs. The analog inputs are applied to these terminals and are internally

multiplexed. The driving source impedance should be less than or equal to 1 k

.

For a source impedance greater than 1 k

, use the asynchronous conversion start signal CSTART

(CSTART low time controls the sampling period) or program long sampling period to increase the

sampling time.

CS

16

20

I

Chip select. A high-to-low transition on the CS input resets the internal 4-bit counter, enables SDI,

and removes SDO from 3-state within a maximum setup time. SDI is disabled within a setup time

after the 4-bit counter counts to 16 (clock edges) or a low-to-high transition of CS whichever

happens first.

NOTE: CS falling and rising edges need to happen when SCLK is low for a microprocessor interface

such as SPI.

CSTART

10

14

I

This terminal controls the start of sampling of the analog input from a selected multiplex channel.

Sampling time starts with the falling edge of CSTART and ends with the rising edge of CSTART as

long as CS is held high. In mode 01, select cycle, CSTART can be issued as soon as CHANNEL

is selected which means the fifth SCLK during the select cycle, but the effective sampling time is

not started until CS goes to high. The rising edge of CSTART (when CS = 1) also starts the

conversion. Tie this terminal to VCC if not used.

EOC/(INT)

4

O

End of conversion or interrupt to host processor.

[PROGRAMMED AS EOC]: This output goes from a high-to-low logic level at the end of the

sampling period and remains low until the conversion is complete and data are ready for transfer.

EOC is used in conversion mode 00 only.

[PROGRAMMED AS INT]: This pin can also be programmed as an interrupt output signal to the host

processor. The falling edge of INT indicates data are ready for output. The following CS

↓ or FS

clears INT.

FS

13

17

I

DSP frame sync input. Indication of the start of a serial data frame in or out of the device. If FS

remains low after the falling edge of CS, SDI is not enabled until an active FS is presented. A

high-to-low transition on the FS input resets the internal 4-bit counter and enables SDI within a

maximum setup time. SDI is disabled within a setup time after the 4-bit counter counts to 16 (clock

edges) or a low-to-high transition of CS whichever happens first.

Tie this terminal to VCC if not used. See the date code information section, item (1).

GND

11

15

I

Ground return for the internal circuitry. Unless otherwise noted, all voltage measurements are with

respect to GND.

PWDN

12

16

I

Both analog and reference circuits are powered down when this pin is at logic zero. The device can

be restarted by active CS, FS or CSTART after this pin is pulled back to logic one.

SCLK

3

I

Input serial clock. This terminal receives the serial SCLK from the host processor. SCLK is used to

clock the input SDI to the input register. When programmed, it may also be used as the source of

the conversion clock.

NOTE: This device supports CPOL (clock polarity) = 0, which is SCLK returns to zero when idling

for SPI compatible interface.

SDI

2

I

Serial data input. The input data is presented with the MSB (D15) first. The first 4-bit MSBs,

D(1512) are decoded as one of the 16 commands (12 only for the TLV2544). The configure write

commands require an additional 12 bits of data.

When FS is not used (FS =1), the first MSB (D15) is expected after the falling edge of CS and is

latched in on the rising edges of SCLK (after CS

↓).

When FS is used (typical with an active FS from a DSP) the first MSB (D15) is expected after the

falling edge of FS and is latched in on the falling edges of SCLK.

SDI is disabled within a setup time after the 4-bit counter counts to 16 (clock edges) or a low-to-high

transition of CS whichever happens first.

相關PDF資料 |

PDF描述 |

|---|---|

| TLV2548IDWRG4 | 8-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2548IPWRG4 | 8-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2544CDR | 4-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO16 |

| TLV2548CDW | 8-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2544CDG4 | 4-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO16 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLV2548CDWR | 功能描述:模數轉換器 - ADC 12-Bit 200 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2548CDWRG4 | 功能描述:模數轉換器 - ADC 12-Bit 200 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2548CPW | 功能描述:模數轉換器 - ADC 12bit 200kSPS ADC RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2548CPWG4 | 功能描述:模數轉換器 - ADC 12-Bit 200 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2548CPWR | 功能描述:模數轉換器 - ADC 12-Bit 200 kSPS Serial Out RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

發布緊急采購,3分鐘左右您將得到回復。