- 您現在的位置:買賣IC網 > PDF目錄98252 > TLV2556IPWG4 (TEXAS INSTRUMENTS INC) 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 PDF資料下載

參數資料

| 型號: | TLV2556IPWG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| 封裝: | GREEN, PLASTIC, TSSOP-20 |

| 文件頁數: | 23/37頁 |

| 文件大小: | 729K |

| 代理商: | TLV2556IPWG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁當前第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁

TLV2556

SLAS355A – DECEMBER 2001 – REVISED SEPTEMBER 2002

3

www.ti.com

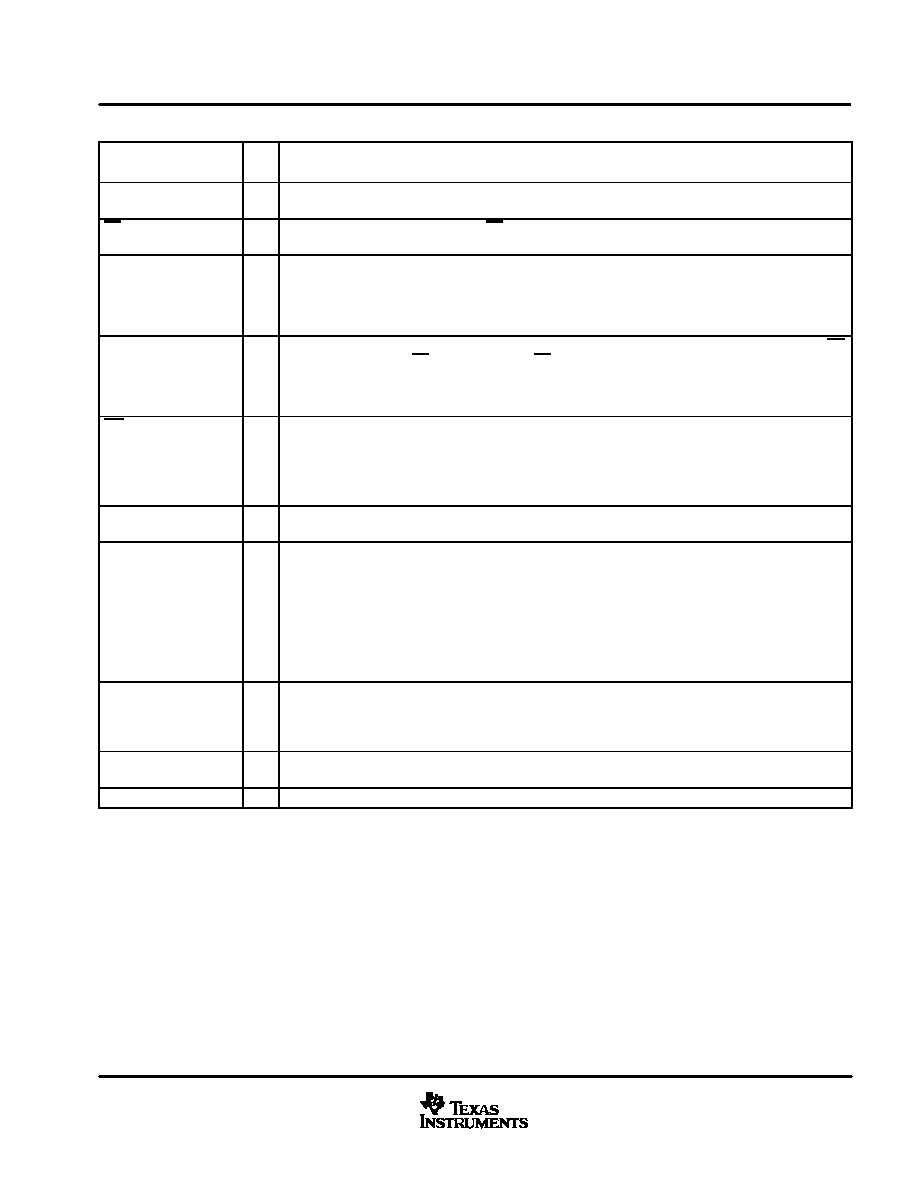

Terminal Functions

TERMINAL

I/O

DESCRIPTION

NAME

NO.

I/O

DESCRIPTION

AIN0 – AIN10

1 – 9,

11, 12

I

Analog input. These 11 analog-signal inputs are internally multiplexed.

CS

15

I

Chip select. A high-to-low transition on CS resets the internal counters and controls and enables DATA OUT,

DATA IN, and I/O CLOCK. A low-to-high transition disables DATA IN and I/O CLOCK within a setup time.

DATA IN

17

I

Serial data input. The 4-bit serial data can be used as address selects the desired analog input channel or

test voltage to be converted next, or a command to activate other other features. The input data is presented

with the MSB (D7) first and is shifted in on the first four rising edges of the I/O CLOCK. After the four

address/command bits are read into the command register CMR, I/O CLOCK clocks the remaining four bits

of configuration in.

DATA OUT

16

O

The 3-state serial output for the A/D conversion result. DATA OUT is in the high-impedance state when CS

is high and active when CS is low. With a valid CS, DATA OUT is removed from the high-impedance state

and is driven to the logic level corresponding to the MSB(most significant bit)/LSB(least significant bit) value

of the previous conversion result. The next falling edge of I/O CLOCK drives DATA OUT to the logic level

corresponding to the next MSB/LSB, and the remaining bits are shifted out in order.

INT/EOC

19

O

Status output, used to indicate the end of conversion (EOC) or an interrupt (INT) to host processor.

Programmed as INT (interrupt): INT goes from a high to a low logic level after the conversion is complete and

the data is ready for transfer. INT is cleared by a rising I/O CLOCK transition.

Programmed as EOC: EOC goes from a high to a low logic level after the falling edge of the last I/O CLOCK

and remains low until the conversion is complete and the data is ready for transfer.

GND

10

Ground. GND is the ground return terminal for the internal circuitry. Unless otherwise noted, all voltage

measurements are with respect to GND.

I/O CLOCK

18

I

Input /output clock. I/O CLOCK receives the serial input and performs the following four functions:

1. It clocks the eight input data bits into the input data register on the first eight rising edges of I/O CLOCK

with the multiplexer address available after the fourth rising edge.

2. On the fourth falling edge of I/O CLOCK, the analog input voltage on the selected multiplexer input

begins charging the capacitor array and continues to do so until the last falling edge of I/O CLOCK.

3. The remaining 11 bits of the previous conversion data are shifted out on DATA OUT. Data changes on the

falling edge of I/O CLOCK.

4. Control of the conversion is transferred to the internal state controller on the falling edge of the last

I/O CLOCK.

REF +

14

I/O

Positive reference voltage The upper reference voltage value (nominally VCC) is applied to REF+. The

maximum analog input voltage range is determined by the difference between the voltage applied to terminals

REF+ and REF–.

When the internal reference is used it is capable of driving a 10-k

, 10-pF load.

REF –

13

I/O

Negative reference voltage. The lower reference voltage value (nominally ground) is applied to REF–. This

pin is connected to analog ground (GND of the ADC) when the internal reference is used.

VCC

20

Positive supply voltage

相關PDF資料 |

PDF描述 |

|---|---|

| TLV2556MPWREP | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV2556MPWREPG4 | 11-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, SERIAL ACCESS, PDSO20 |

| TLV320ADC3001IYZHT | 2-CH 16-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, PBGA16 |

| TLV320ADC3001IYZHR | 2-CH 16-BIT PROPRIETARY METHOD ADC, SERIAL ACCESS, PBGA16 |

| TLV320ADC3101IRGER320 | SPECIALTY CONSUMER CIRCUIT, PQCC24 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLV2556IPWR | 功能描述:模數轉換器 - ADC 12-Bit 200 KSPS 11 Ch Lo-Pwr RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2556IPWRG4 | 功能描述:模數轉換器 - ADC 12-Bit 200 KSPS 11 Ch Lo-Pwr RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2556MPWREP | 功能描述:模數轉換器 - ADC EP 12B,200KSPS,11Ch Low Pwr,Serial ADC RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2556MPWREPG4 | 功能描述:模數轉換器 - ADC EP 12B,200KSPS,11Ch RoHS:否 制造商:Texas Instruments 通道數量:2 結構:Sigma-Delta 轉換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV2620ID | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發布緊急采購,3分鐘左右您將得到回復。