- 您現在的位置:買賣IC網 > PDF目錄98253 > TLV320AIC23BPWRG4 (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PDSO28 PDF資料下載

參數資料

| 型號: | TLV320AIC23BPWRG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 封裝: | GREEN, PLASTIC, TSSOP-28 |

| 文件頁數: | 19/54頁 |

| 文件大小: | 795K |

| 代理商: | TLV320AIC23BPWRG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁當前第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁

37

This minimizes audible clicks as the volume is changed or the device is muted. This circuit has no time-out, so, if only

dc levels are being applied to the gain stage input of more than 20 mV, the gain is not updated.

The gain is independently programmable on the left and right channels. Both channels can be locked to the same

value by setting the RLS and LRS bits (see Section 3.1.3).

3.2.5

Analog Bypass Mode

The TLV320AIC23B includes a bypass mode in which the analog line inputs are directly routed to the analog line

outputs, bypassing the ADC and DAC. This is enabled by selecting the bypass bit in the analog audio path control

register[see Section 3.1.3).

For a true bypass mode, the output from the DAC and the sidetone should be disabled. The line input and headphone

output volume controls and mutes are still operational in bypass mode. Therefore the line inputs, DAC output, and

microphone input can be summed together. The maximum signal at any point in the bypass path must be no greater

than 1.0Vrms at AVDD=3.3V to avoid clipping and distortion. This amplitude tracks linearly with AVDD.

3.2.6

Sidetone Insertion

The TLV320AIC23B has a sidetone insertion made where the microphone input is routed to the line and headphone

outputs. This is useful for telephony and headset applications. The attenuation of the sidetone signal may be set to

6 dB, 9 dB, 12 dB, 15 dB, or 0dB, by software selection (see Section 3.1.3). If this mode is used to sum the

microphone input with the DAC output and line inputs, care must be taken not to exceed signal level to avoid clipping

and distortion.

3.3

Digital Audio Interface

3.3.1

Digital Audio-Interface Modes

The TLV320AIC23B supports four audio-interface modes.

Right justified

Left justified

I2S mode

DSP mode

The four modes are MSB first and operate with a variable word width between 16 to 32 bits (except right-justified

mode, which does not support 32 bits).

The digital audio interface consists of clock signal BCLK, data signals DIN and DOUT, and synchronization signals

LRCIN and LRCOUT. BCLK is an output in master mode and an input in slave mode.

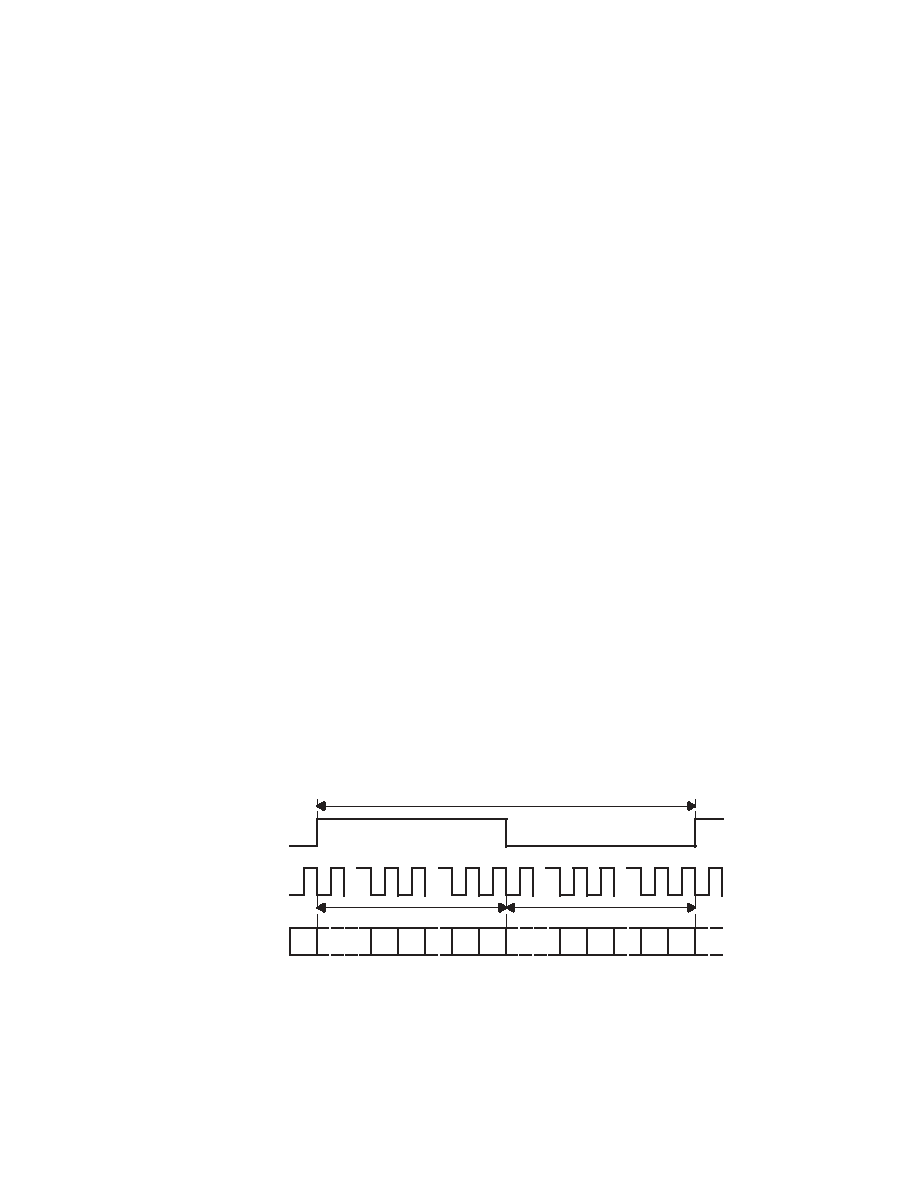

3.3.1.1 Right-Justified Mode

In right-justified mode, the LSB is available on the rising edge of BCLK, preceding a falling edge on LRCIN or LRCOUT

(see Figure 3-5).

LRCIN/

BCLK

DIN/

n

n1

0

1

n1

n

1/fs

Left Channel

Right Channel

1

0

MSB

LSB

LRCOUT

DOUT

Figure 35. Right-Justified Mode Timing

3.3.1.2 Left-Justified Mode

In left-justified mode, the MSB is available on the rising edge of BCLK, following a rising edge on LRCIN or LRCOUT

(see Figure 3-6)

相關PDF資料 |

PDF描述 |

|---|---|

| TLV320AIC23BRHDG4 | SPECIALTY CONSUMER CIRCUIT, PQCC28 |

| TLV320A23BIRHDRG4 | SPECIALTY CONSUMER CIRCUIT, PQCC28 |

| TLV320AIC23BRHDRG4 | SPECIALTY CONSUMER CIRCUIT, PQCC28 |

| TLV320AIC23BIRHDG4 | SPECIALTY CONSUMER CIRCUIT, PQCC28 |

| TLV320AIC23BIPWG4 | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLV320AIC23B-Q1 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Stereo Audio Codec, 8- to 96-kHz, With Integrated Headphone Amplifier |

| TLV320AIC23BRHD | 功能描述:接口—CODEC Lo-Pwr Highly Integrated Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC23BRHDG4 | 功能描述:接口—CODEC L-P Stereo CODEC with HP Amplifier RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC23BRHDR | 功能描述:接口—CODEC Lo-Pwr Highly Integrated Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TLV320AIC23BRHDRG4 | 功能描述:接口—CODEC Lo-Pwr Highly Integrated Codec RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

發布緊急采購,3分鐘左右您將得到回復。