- 您現在的位置:買賣IC網 > PDF目錄98260 > TLV5624CDR (TEXAS INSTRUMENTS INC) SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 8-BIT DAC, PDSO8 PDF資料下載

參數資料

| 型號: | TLV5624CDR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | DAC |

| 英文描述: | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 8-BIT DAC, PDSO8 |

| 封裝: | GREEN, PLASTIC, MS-012AA, SOIC-8 |

| 文件頁數: | 18/22頁 |

| 文件大小: | 571K |

| 代理商: | TLV5624CDR |

TLV5624

2.7V TO 5.5V LOW POWER 8BIT DIGITALTOANALOG

CONVERTER WITH INTERNAL REFERENCE AND POWER DOWN

SLAS235B JULY 1999 REVISED APRIL 2004

5

WWW.TI.COM

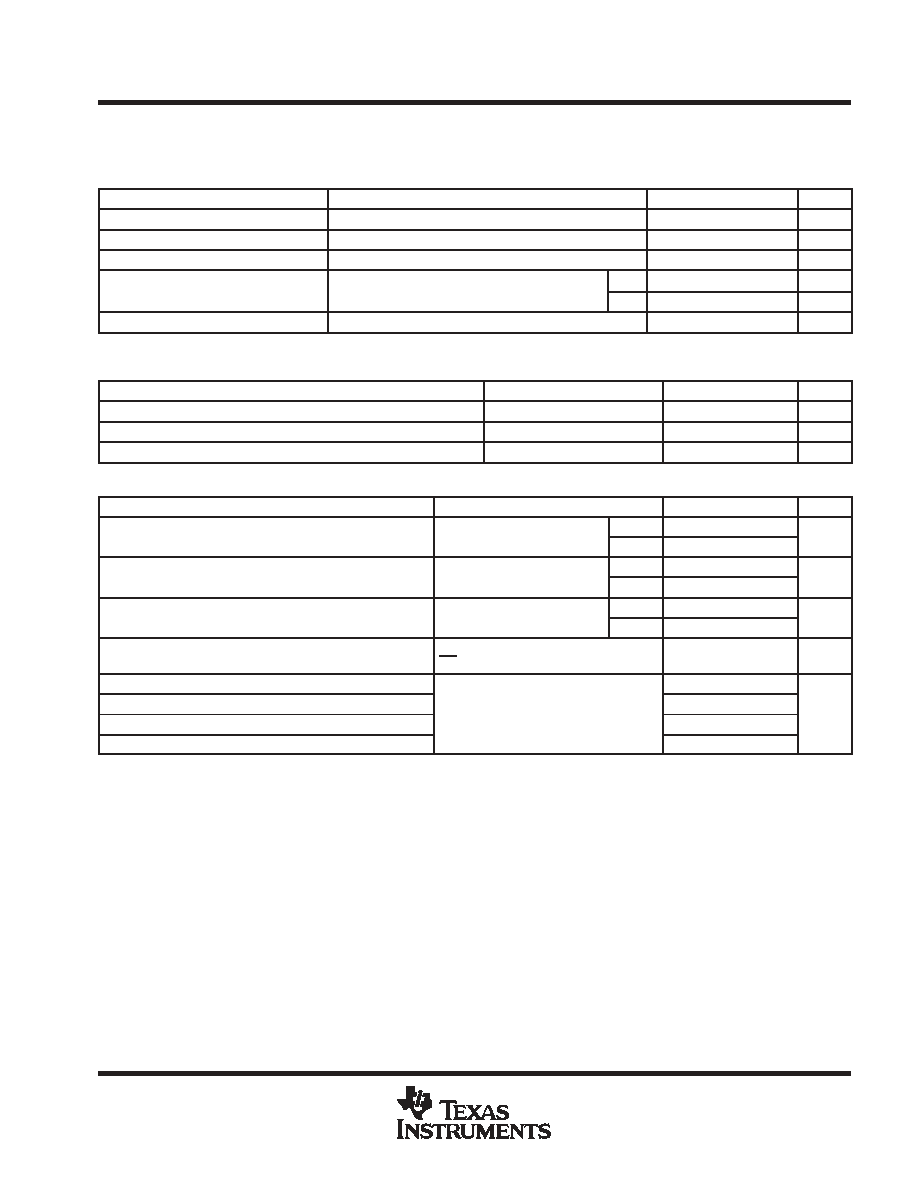

electrical characteristics over recommended operating conditions (unless otherwise noted)

(Continued)

reference pin configured as input (REF)

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

VI

Input voltage

0

VDD1.5

V

RI

Input resistance

10

M

CI

Input capacitance

5

pF

Reference input bandwidth

REF = 0.2 Vpp + 1.024 V dc

Fast

1.3

MHz

Reference input bandwidth

REF = 0.2 Vpp + 1.024 V dc

Slow

525

kHz

Reference feedthrough

REF = 1 Vpp at 1 kHz + 1.024 V dc (see Note 10)

80

dB

NOTE 10: Reference feedthrough is measured at the DAC output with an input code = 0x000.

digital inputs

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

IIH

High-level digital input current

VI = VDD

1

A

IIL

Low-level digital input current

VI = 0 V

1

A

Ci

Input capacitance

8

pF

analog output dynamic performance

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

ts(FS)

Output settling time, full scale

RL = 10 k,CL = 100 pF,

Fast

1

3

s

ts(FS)

Output settling time, full scale

RL = 10 k,CL = 100 pF,

See Note 11

Slow

3.5

7

s

ts(CC)

Output settling time, code to code

RL = 10 k,CL = 100 pF,

Fast

0.5

1.5

s

ts(CC)

Output settling time, code to code

RL = 10 k,CL = 100 pF,

See Note 12

Slow

1

2

s

SR

Slew rate

RL = 10 k,CL = 100 pF,

Fast

8

V/ s

SR

Slew rate

RL = 10 k,CL = 100 pF,

See Note 13

Slow

1.5

V/

s

Glitch energy

DIN = 0 to 1,

fCLK = 100 kHz,

CS = VDD

5

nVS

SNR

Signal-to-noise ratio

53

57

S/(N+D)

Signal-to-noise + distortion

fs = 480 kSPS, fout = 1 kHz,

48

47

dB

THD

Total harmonic distortion

fs = 480 kSPS, fout = 1 kHz,

RL = 10 k,CL = 100 pF

50

48

dB

Spurious free dynamic range

RL = 10 k ,CL = 100 pF

50

62

NOTES: 11. Settling time is the time for the output signal to remain within

±0.5 LSB of the final measured value for a digital input code change

of 0x020 to 0xFDFand 0xFDF to 0x020 respectively. Not tested, assured by design.

12. Settling time is the time for the output signal to remain within

± 0.5 LSB of the final measured value for a digital input code change

of one count. Not tested, assured by design.

13. Slew rate determines the time it takes for a change of the DAC output from 10% to 90% full-scale voltage.

相關PDF資料 |

PDF描述 |

|---|---|

| TLV5624IDGKR | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 8-BIT DAC, PDSO8 |

| TLV5624IDR | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 8-BIT DAC, PDSO8 |

| TLV5624IDGKG4 | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 8-BIT DAC, PDSO8 |

| TLV5624CDG4 | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 8-BIT DAC, PDSO8 |

| TLV5624CDGKR | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 8-BIT DAC, PDSO8 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLV5624CDRG4 | 功能描述:數模轉換器- DAC 8-Bit 1.0-3.5us DAC Serial Out RoHS:否 制造商:Texas Instruments 轉換器數量:1 DAC 輸出端數量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| TLV5624D | 制造商:TI 制造商全稱:Texas Instruments 功能描述:2.7 V TO 5.5 V LOW POWER 8-BIT DIGITAL-TO-ANALOG CONVERTER WITH INTERNAL REFERENCE AND POWER DOWN |

| TLV5624DGK | 制造商:TI 制造商全稱:Texas Instruments 功能描述:2.7 V TO 5.5 V LOW POWER 8-BIT DIGITAL-TO-ANALOG CONVERTER WITH INTERNAL REFERENCE AND POWER DOWN |

| TLV5624ID | 功能描述:數模轉換器- DAC 8bit DAC w/Pwr D RoHS:否 制造商:Texas Instruments 轉換器數量:1 DAC 輸出端數量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| TLV5624IDG4 | 功能描述:數模轉換器- DAC 8-Bit 1.0-3.5us DAC Serial Out RoHS:否 制造商:Texas Instruments 轉換器數量:1 DAC 輸出端數量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

發布緊急采購,3分鐘左右您將得到回復。