- 您現在的位置:買賣IC網 > PDF目錄98261 > TLV5630IDWRG4 (TEXAS INSTRUMENTS INC) SERIAL INPUT LOADING, 3 us SETTLING TIME, 12-BIT DAC, PDSO20 PDF資料下載

參數資料

| 型號: | TLV5630IDWRG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | DAC |

| 英文描述: | SERIAL INPUT LOADING, 3 us SETTLING TIME, 12-BIT DAC, PDSO20 |

| 封裝: | GREEN, PLASTIC, SOIC-20 |

| 文件頁數: | 3/21頁 |

| 文件大小: | 565K |

| 代理商: | TLV5630IDWRG4 |

www.ti.com

SERIAL CLOCK FREQUENCY AND UPDATE RATE

f

sclkmax +

1

t

whmin )

t

wlmin

+ 30 MHz

f

updatemax +

1

16 t

whmin )

t

wlmin

+ 1.95 MHz

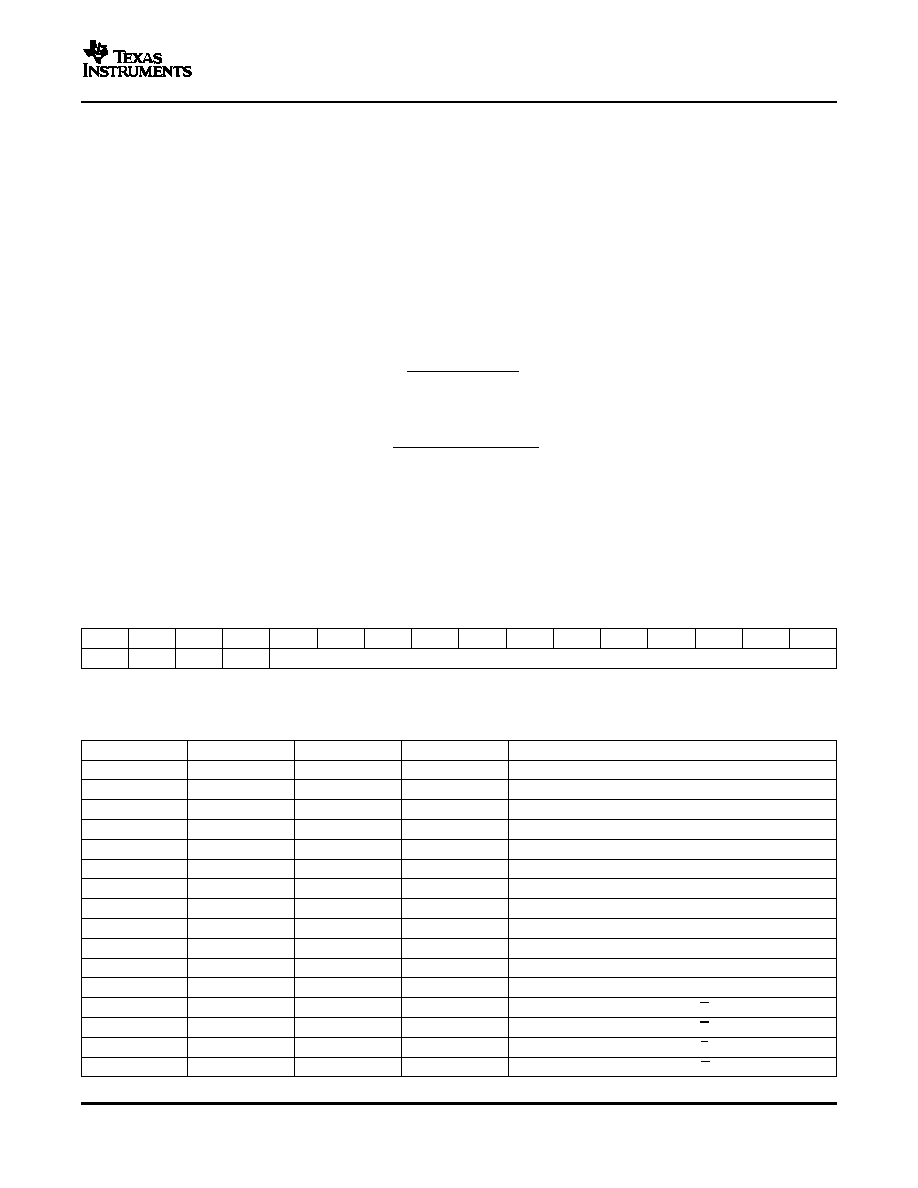

DATA FORMAT

TLV5630

TLV5631

TLV5632

SLAS269E – MAY 2000 – REVISED JUNE 2005

APPLICATION INFORMATION (continued)

Difference between DSP mode (MODE = N.C. or 0) and C (MODE = 1) mode:

In C mode, FS needs to be held low until all 16 data bits have been transferred. If FS is driven high before

the 16th falling clock edge, the data transfer is cancelled. The DAC is updated after a rising edge on FS.

In DSP mode, FS needs to stay low for 20 ns and can go high before the 16th falling clock edge.

In DSP mode there needs to be one falling SCLK edge before FS goes low to start the write (DIN) cycle.

This extra falling SCLK edge has to happen at least 5 ns before FS goes low, t

su(CK-FS) ≥ 5 ns.

In C mode, the extra falling SCLK edge is not necessary. However, if it does happen, the extra negative

SCLK edge is not allowed to occur within 10 ns after FS goes HIGH to finish the WRITE cycle (t

su(FS-C17)).

The maximum serial clock frequency is given by:

The maximum update rate is:

Note, that the maximum update rate is just a theoretical value for the serial interface, as the settling time of the

DAC has to be considered also.

The 16-bit data word consists of two parts:

Address bits (D15

…D12)

Data bits (D11

…D0)

D15

D14

D13

D12

D11

D10

D9

D8

D7

D6

D5

D4

D3

D2

D1

D0

A3

A2

A1

A0

Data

Ax: Address bits. See table.

REGISTER MAP

A3

A2

A1

A0

FUNCTION

0

DAC A

0

1

DAC B

0

1

0

DAC C

0

1

DAC D

0

1

0

DAC E

0

1

0

1

DAC F

0

1

0

DAC G

0

1

DAC H

1

0

CTRL0

1

0

1

CTRL1

1

0

1

0

Preset

1

0

1

Reserved

1

0

DAC A and B

1

0

1

DAC C and D

1

0

DAC E and F

1

DAC G and H

11

相關PDF資料 |

PDF描述 |

|---|---|

| TLV5630IDWR | SERIAL INPUT LOADING, 3 us SETTLING TIME, 12-BIT DAC, PDSO20 |

| TLV5631IDW | SERIAL INPUT LOADING, 3 us SETTLING TIME, 10-BIT DAC, PDSO20 |

| TLV5631IPW | SERIAL INPUT LOADING, 3 us SETTLING TIME, 10-BIT DAC, PDSO20 |

| TLV5631IPWR | SERIAL INPUT LOADING, 3 us SETTLING TIME, 10-BIT DAC, PDSO20 |

| TLV5631IPWG4 | SERIAL INPUT LOADING, 3 us SETTLING TIME, 10-BIT DAC, PDSO20 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLV5630IPW | 功能描述:數模轉換器- DAC 12bit 8Chl DAC RoHS:否 制造商:Texas Instruments 轉換器數量:1 DAC 輸出端數量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| TLV5630IPW | 制造商:Texas Instruments 功能描述:IC's |

| TLV5630IPWG4 | 功能描述:數模轉換器- DAC 2.7V to 5.5V 12-Bit 8-Ch Ser W/Int Ref RoHS:否 制造商:Texas Instruments 轉換器數量:1 DAC 輸出端數量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| TLV5630IPWR | 功能描述:數模轉換器- DAC 2.7V to 5.5V 12-Bit 8-Ch Ser W/Int Ref RoHS:否 制造商:Texas Instruments 轉換器數量:1 DAC 輸出端數量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| TLV5630IPWRG4 | 功能描述:數模轉換器- DAC 2.7V to 5.5V 12-Bit 8-Ch Ser W/Int Ref RoHS:否 制造商:Texas Instruments 轉換器數量:1 DAC 輸出端數量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

發布緊急采購,3分鐘左右您將得到回復。