- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98261 > TLV5633CDWR (TEXAS INSTRUMENTS INC) PARALLEL, WORD INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO20 PDF資料下載

參數(shù)資料

| 型號(hào): | TLV5633CDWR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | DAC |

| 英文描述: | PARALLEL, WORD INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO20 |

| 封裝: | GREEN, PLASTIC, SOIC-20 |

| 文件頁(yè)數(shù): | 4/25頁(yè) |

| 文件大小: | 486K |

| 代理商: | TLV5633CDWR |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)

www.ti.com

DATA FORMAT

LAYOUT CONSIDERATIONS

SLAS190C – MARCH 1999 – REVISED SEPTEMBER 2006

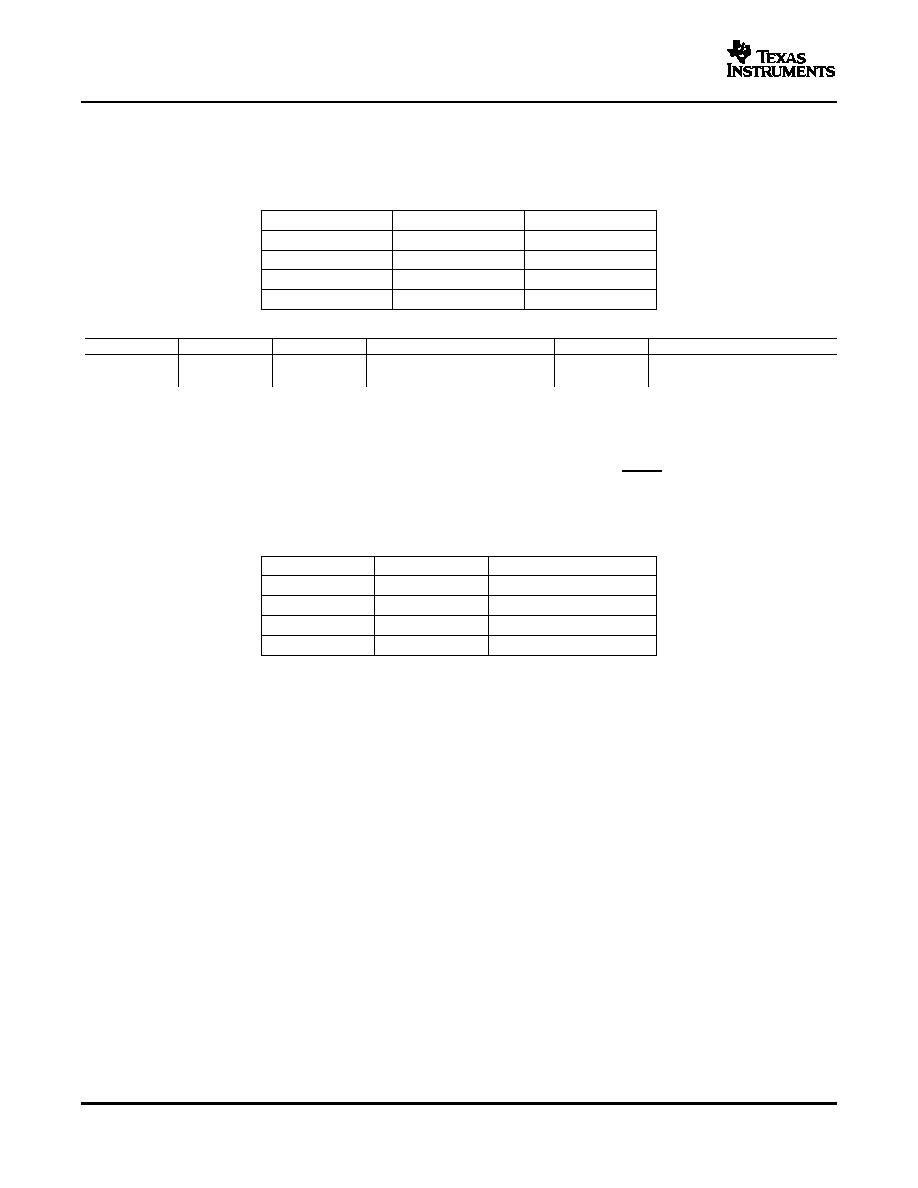

The TLV5633 writes data either to one of the DAC holding latches or to the control register depending on the

address bits A1 and A0.

ADDRESS BITS

A1

A0

REGISTER

0

DAC LSW holding

0

1

DAC MSW holding

1

0

Reserved

1

Control

The following table lists the meaning of the bits within the control register.

D7

D6

D5

D4

D3

D2

D1

D0

X

REF1

REF0

RLDAC

PWR

SPD

X(1)

0(1)

(1)

Default values: X = Don't Care

SPD: Speed control bit

1

→ fast mode

0

→ slow mode

PWR: Power control bit

1

→ power down

0

→ normal operation

RLDAC: Load DAC latch

1

→ latch transparent 0 → DAC latch controlled by LDAC pin

REF1 and REF0 determine the reference source and the reference voltage.

REFERENCE BITS

REF1

REF0

REFERENCE

0

External

0

1

1.024 V

1

0

2.048 V

1

External

If an external reference voltage is applied to the REF pin, external reference must be selected.

To achieve the best performance, it is recommended to have separate power planes for GND, AVDD, and DVDD.

Figure 13 shows how to lay out the power planes for the TLV5633. As a general rule, digital and analog signals

should be separated as wide as possible. To avoid crosstalk, analog and digital traces must not be routed in

parallel. The two positive power planes (AVDD and DVDD) should be connected together at one point with a

ferrite bead.

A 100-nF ceramic low series inductance capacitor between DVDD and GND and a 1-F tantalum capacitor

between AVDD and GND placed as close as possible to the supply pins are recommended for optimal

performance.

12

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TLV5633IPWR | PARALLEL, WORD INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO20 |

| TLV5633IDWG4 | PARALLEL, WORD INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO20 |

| TLV5633CDWG4 | PARALLEL, WORD INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO20 |

| TLV5633CPWRG4 | PARALLEL, WORD INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO20 |

| TLV5633CPWG4 | PARALLEL, WORD INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO20 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TLV5633CDWRG4 | 功能描述:數(shù)模轉(zhuǎn)換器- DAC 2.7-5.5-V Low Power 12-Bit DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| TLV5633CPW | 功能描述:數(shù)模轉(zhuǎn)換器- DAC 2.7-5.5-V Low Power 12-Bit DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| TLV5633CPWG4 | 功能描述:數(shù)模轉(zhuǎn)換器- DAC 2.7-5.5-V Low Power 12-Bit DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| TLV5633CPWR | 功能描述:數(shù)模轉(zhuǎn)換器- DAC 2.7-5.5-V Low Power 12-Bit DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| TLV5633CPWRG4 | 功能描述:數(shù)模轉(zhuǎn)換器- DAC 2.7-5.5-V Low Power 12-Bit DAC RoHS:否 制造商:Texas Instruments 轉(zhuǎn)換器數(shù)量:1 DAC 輸出端數(shù)量:1 轉(zhuǎn)換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩(wěn)定時(shí)間:1 us 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。