- 您現在的位置:買賣IC網 > PDF目錄98262 > TLV5636CDRG4 (TEXAS INSTRUMENTS INC) SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO8 PDF資料下載

參數資料

| 型號: | TLV5636CDRG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | DAC |

| 英文描述: | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO8 |

| 封裝: | GREEN, PLASTIC, MS-012AA, SOIC-8 |

| 文件頁數: | 19/23頁 |

| 文件大小: | 521K |

| 代理商: | TLV5636CDRG4 |

www.ti.com

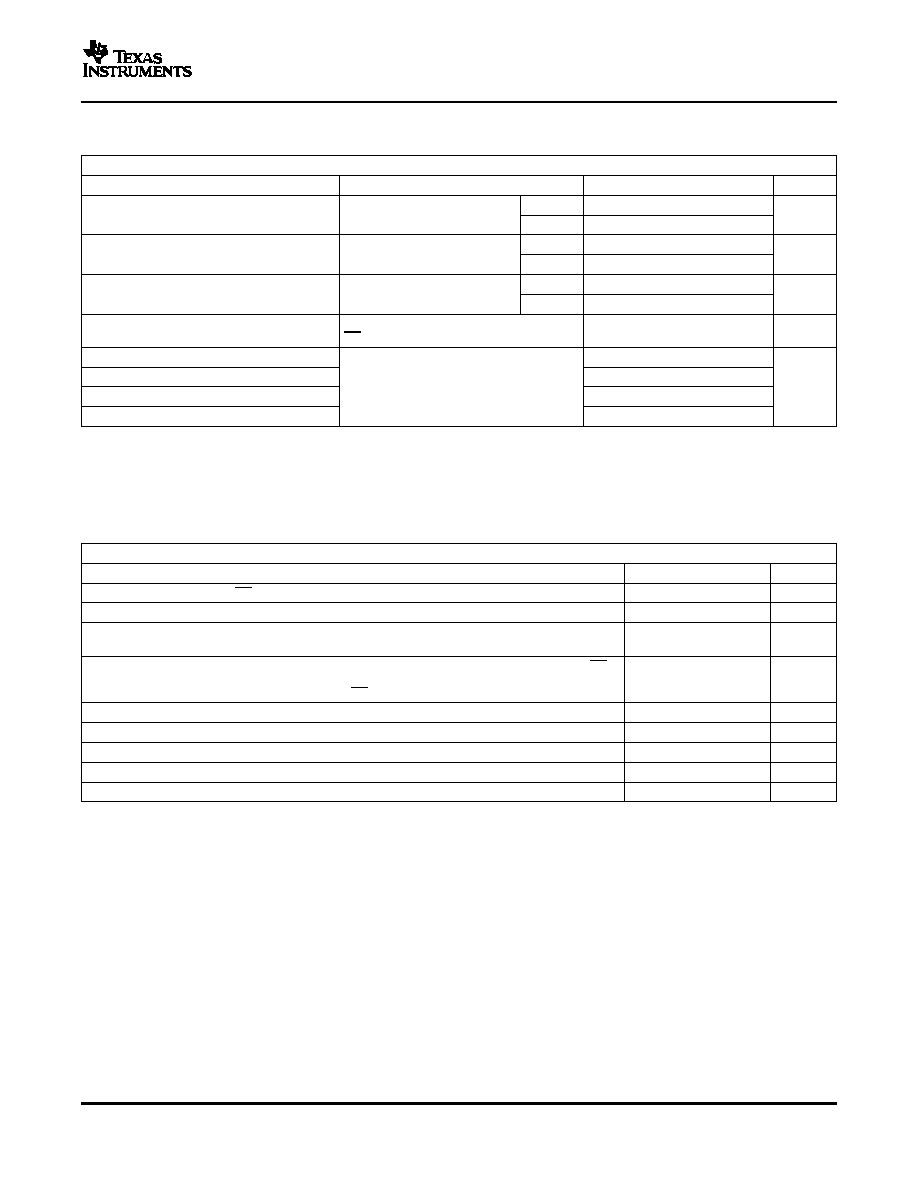

ELECTRICAL CHARACTERISTICS

TIMING REQUIREMENTS

TLV5636

SLAS223C – JUNE 1999 – REVISED APRIL 2004

over recommended operating free-air temperature range, supply voltages, and reference voltages (unless otherwise noted)

ANALOG OUTPUT DYNAMIC PERFORMANCE

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Fast

1

3

RL = 10 k,

ts(FS)

Output settling time (full scale)

CL = 100 pF,

s

see note(1)

Slow

3.5

7

Fast

0.5

1.5

RL = 10 k,

ts(CC)

Output settling time, code to code

CL = 100 pF,

s

see note(2)

Slow

1

2

Fast

8

RL = 10 k,

SR

Slew rate

CL = 100 pF,

V/s

see note(3)

Slow

1.5

DIN = 0 to 1,

fout = 1 kHz,

Glitch energy

5

nV-s

CS = VDD

SNR

Signal-to-noise ratio

71

75

S/(N+D)

Signal-to-noise + distortion

59

66

fs = 480 kSPS,

fout = 1 kHz,

dB

RL = 10 k,

CL = 100 pF

THD

Total harmonic distortion

-67

-59

Spurious free dynamic range

59

69

(1)

Settling time is the time for the output signal to remain within +0.5 LSB of the final measured value for a digital input code change of

0x20 to 0xFDF and 0xFDF to 0x020 respectively. Assured by design; not tested.

(2)

Settling time is the time for the output signal to remain within +0.5 LSB of the final measured value for a digital input code change of one

count. Assured by design; not tested.

(3)

Slew rate determines the time it takes for a change of the DAC output from 10% to 90% full-scale voltage.

DIGITAL INPUTS

MIN

NOM

MAX

UNIT

tsu(CS-FS)

Setup time, CS low before FS falling edge

10

ns

tsu(FS-CK)

Setup time, FS low before first negative SCLK edge

8

ns

Setup time, 16th negative edge after FS low on which bit D0 is sampled before

tsu(C16-FS)

10

ns

rising edge of FS.

Setup time, 16th positive SCLK edge (first positive after D0 is sampled) before CS

tsu(C16-CS)

rising edge. If FS is used instead of 16th positive edge to update DAC, then setup

10

ns

time between FS rising edge and CS rising edge.

twH

SCLK pulse duration high

25

ns

twL

SCLK pulse duration low

25

ns

tsu(D)

Setup time, data ready before SCLK falling edge

8

ns

th(D)

Hold time, data held valid after SCLK falling edge

5

ns

twH(FS)

FS duration high

25

ns

5

相關PDF資料 |

PDF描述 |

|---|---|

| TLV5636CDGKRG4 | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO8 |

| TLV5636CD | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO8 |

| TLV5636IDGKRG4 | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO8 |

| TLV5636CDGKG4 | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO8 |

| TLV5636IDG4 | SERIAL INPUT LOADING, 3.5 us SETTLING TIME, 12-BIT DAC, PDSO8 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TLV5636D | 制造商:TI 制造商全稱:Texas Instruments 功能描述:2.7 V TO 5.5 V LOW POWER 12-BIT DIGITAL-TO-ANALOG CONVERTER WITH INTERNAL REFERENCE AND POWER DOWN |

| TLV5636DGK | 制造商:TI 制造商全稱:Texas Instruments 功能描述:2.7 V TO 5.5 V LOW POWER 12-BIT DIGITAL-TO-ANALOG CONVERTER WITH INTERNAL REFERENCE AND POWER DOWN |

| TLV5636ID | 功能描述:數模轉換器- DAC 12bit DAC w/Power D RoHS:否 制造商:Texas Instruments 轉換器數量:1 DAC 輸出端數量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| TLV5636IDG4 | 功能描述:數模轉換器- DAC 12bit DAC w/Power D RoHS:否 制造商:Texas Instruments 轉換器數量:1 DAC 輸出端數量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| TLV5636IDGK | 功能描述:數模轉換器- DAC 12bit DAC w/Power D RoHS:否 制造商:Texas Instruments 轉換器數量:1 DAC 輸出端數量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

發布緊急采購,3分鐘左右您將得到回復。