- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98262 > TLV571IDWRG4 (TEXAS INSTRUMENTS INC) 1-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 PDF資料下載

參數(shù)資料

| 型號: | TLV571IDWRG4 |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | ADC |

| 英文描述: | 1-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 |

| 封裝: | GREEN, PLASTIC, SOIC-24 |

| 文件頁數(shù): | 24/28頁 |

| 文件大小: | 429K |

| 代理商: | TLV571IDWRG4 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁當前第24頁第25頁第26頁第27頁第28頁

TLV571

2.7 V TO 5.5 V, 1-CHANNEL, 8-BIT,

PARALLEL ANALOG-TO-DIGITAL CONVERTER

SLAS239A – SEPTEMBER 1999 – REVISED FEBRUARY 2000

5

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

detailed description (continued)

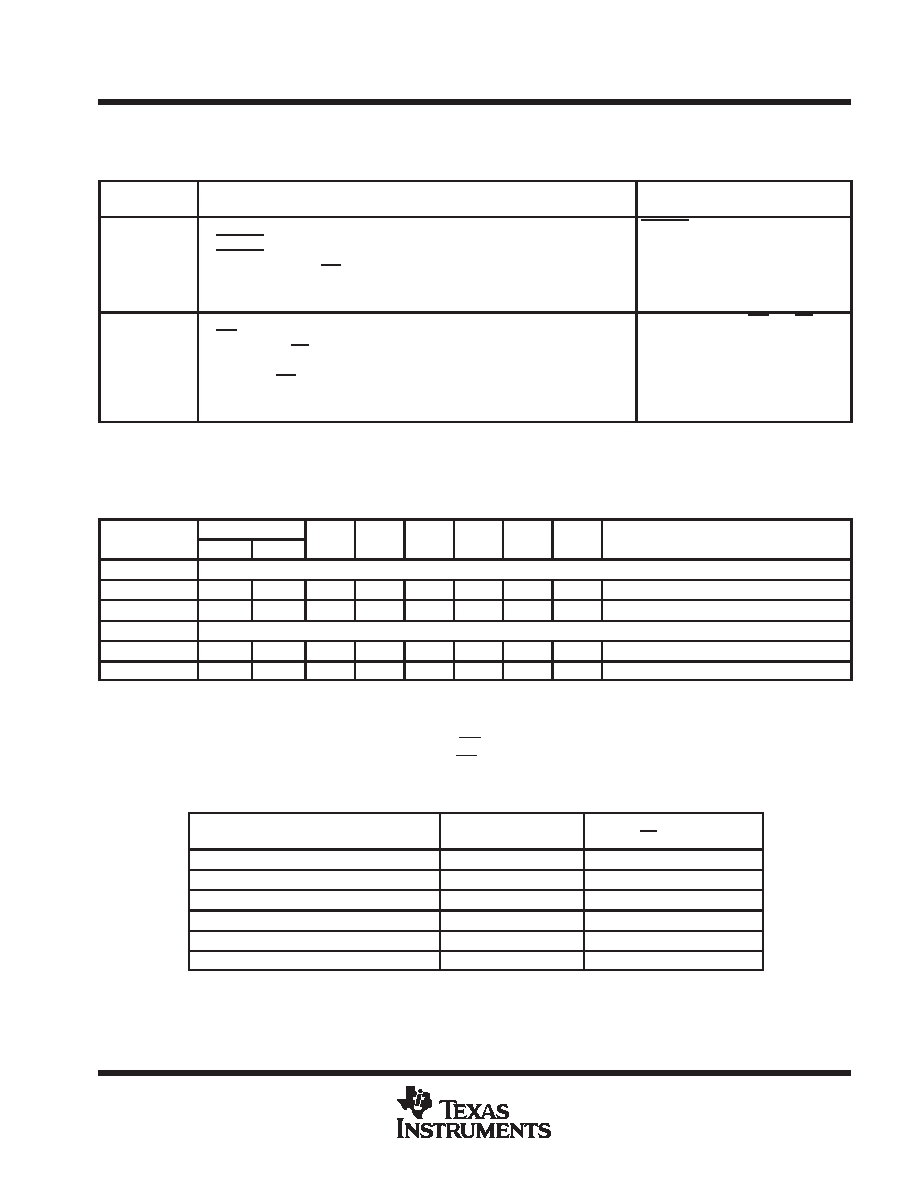

Table 1. Conversion Modes

START OF

CONVERSION

OPERATION

COMMENTS – FOR INPUT

Hardware start

(CSTART)

CR0.D5 = 0

Repeated conversions from AIN

CSTART falling edge to start sampling

CSTART rising edge to start conversion

If in INT mode, one INT pulse generated after each conversion

If in EOC mode, EOC will go high to low at start of conversion, and return high

at end of conversion.

CSTART rising edge must be applied

a minimum of 5 ns before or after CLK

rising edge.

Software start

CR0.D5 = 1

Repeated conversions from AIN

WR rising edge to start sampling initially. Thereafter, sampling occurs at the

rising edge of RD.

Conversion begins after 6 clocks after sampling has begun. Thereafter, if in INT

mode, one INT pulse generated after each conversion

If in EOC mode, EOC will go high to low at start of conversion and return high at

end of conversion.

With external clock, WR and RD rising

edge must be a minimum 5 ns before

or after CLK rising edge.

configure the device

The device can be configured by writing to control registers CR0 and CR1.

Table 2. TLV571 Programming Examples

REGISTER

INDEX

D5

D4

D3

D2

D1

D0

COMMENT

REGISTER

D7

D6

D5

D4

D3

D2

D1

D0

COMMENT

EXAMPLE1

CR0

0

Normal, INT OSC

CR1

0

1

0

Binary

EXAMPLE2

CR0

0

1

0

Power down, EXT OSC

CR1

0

1

0

1

0

2’s complement output

power down

The TLV571 offers two power down modes, auto power down and software power down. This device will

automatically proceed to auto power down mode if RD is not present one clock after conversion. Software power

down is controlled directly by the user by pulling CS to DVDD.

Table 3. Power Down Modes

PARAMETERS/MODES

AUTO POWER DOWN

SOFTWARE POWER DOWN

(CS = DVDD)

Maximum power down dissipation current

1 mA

10

A

Comparator

Power down

Clock buffer

Power down

Control registers

Saved

Minimum power down time

1 CLK

2 CLK

Minimum resume time

1 CLK

2 CLK

相關PDF資料 |

PDF描述 |

|---|---|

| TLV571IDWR | 1-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 |

| TLV571IPWR | 1-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 |

| TLV571IDWG4 | 1-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 |

| TLV571IDW | 1-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 |

| TLV571IPWG4 | 1-CH 8-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, PDSO24 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TLV571IPW | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 8bit SAR A/D RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV571IPWG4 | 功能描述:模數(shù)轉(zhuǎn)換器 - ADC 8-Bit 1.25 MSPS Single Ch. RoHS:否 制造商:Texas Instruments 通道數(shù)量:2 結(jié)構(gòu):Sigma-Delta 轉(zhuǎn)換速率:125 SPs to 8 KSPs 分辨率:24 bit 輸入類型:Differential 信噪比:107 dB 接口類型:SPI 工作電源電壓:1.7 V to 3.6 V, 2.7 V to 5.25 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:VQFN-32 |

| TLV571PW | 制造商:TI 制造商全稱:Texas Instruments 功能描述:2.7 V TO 5.5 V, 1-CHANNEL, 8-BIT, PARALLEL ANALOG-TO-DIGITAL CONVERTER |

| TLV5734 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:TRIPLE 8 BIT 30 MSPS ADC WITH HIGH -PRECISION CLAMP FOR YUV/RGB VIDEO |

| TLV5734PAG | 功能描述:視頻模擬/數(shù)字化轉(zhuǎn)換器集成電路 8B 30MSPS ADC Triple Ch Digital Clamp RoHS:否 制造商:Texas Instruments 輸入信號類型:Differential 轉(zhuǎn)換器數(shù)量:1 ADC 輸入端數(shù)量:4 轉(zhuǎn)換速率:3 Gbps 分辨率:8 bit 結(jié)構(gòu): 輸入電壓:3.3 V 接口類型:SPI 信噪比: 電壓參考: 電源電壓-最大:3.45 V 電源電壓-最小:3.15 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:TCSP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。