- 您現在的位置:買賣IC網 > PDF目錄384013 > TMC2249AKEC2 (FAIRCHILD SEMICONDUCTOR CORP) Digital Mixer 12 x 12 Bit, 60 MHz PDF資料下載

參數資料

| 型號: | TMC2249AKEC2 |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 數字信號處理外設 |

| 英文描述: | Digital Mixer 12 x 12 Bit, 60 MHz |

| 中文描述: | 12-BIT, DSP-MIXER, PQFP120 |

| 封裝: | METRIC, QFP-120 |

| 文件頁數: | 1/18頁 |

| 文件大小: | 138K |

| 代理商: | TMC2249AKEC2 |

www.fairchildsemi.com

REV. 1.0.2 7/6/00

Features

60 MHz input and computation rate

Two 12-bit multipliers

Separate data and coefficient inputs

Independent, user-selectable pipeline delays of 1 to 16

clocks on all input ports

Separate 16-bit input port allows cascading or addition of

a constant

User-selectable rounded output

Internal 1/2 LSB rounding of products

Fully registered, pipelined architecture

Available in 120-Pin CPGA, PPGA, MPGA or MQFP

Applications

Video switching

Image mixing

Digital signal modulation

Complex frequency synthesis

Digital filtering

Complex arithmetic functions

Description

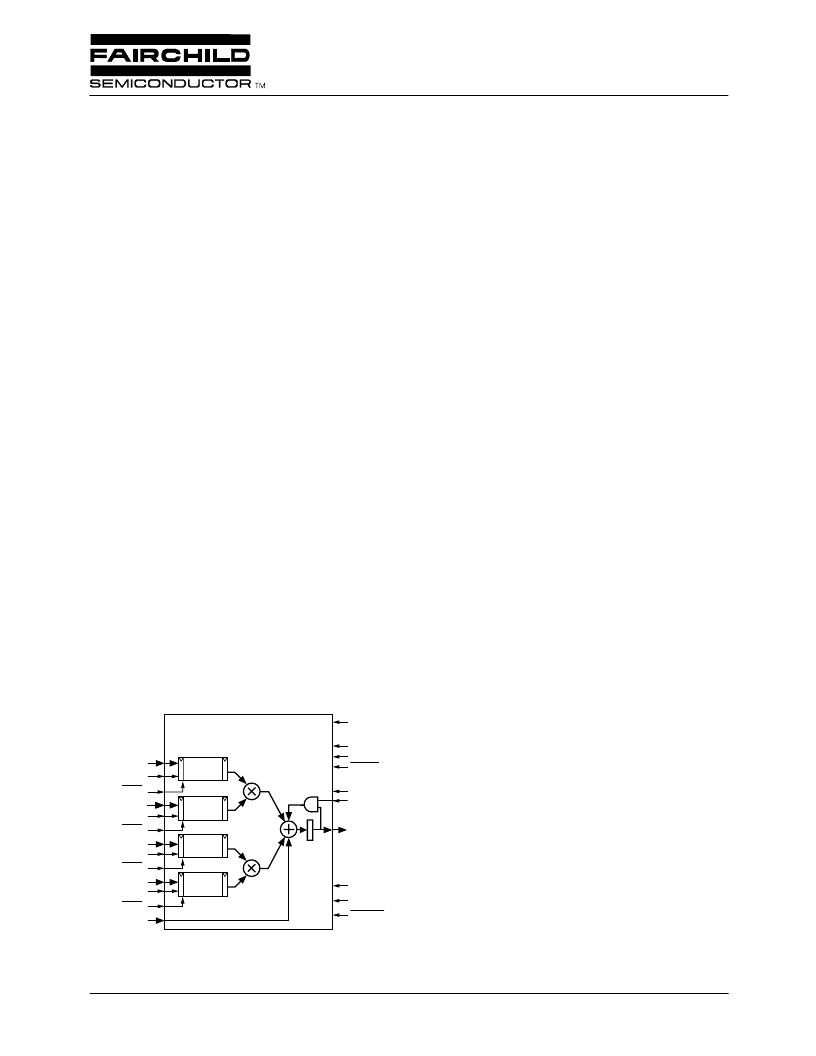

The TMC2249A is a high-speed digital arithmetic circuit

consisting of two 12-bit multipliers, an adder and a cascade-

able accumulator. All four multiplier inputs are simulta-

neously accessible to the user, and each includes a user-

programmable pipeline delay of up to 16 clocks in length.

The 24-bit adder/subtractor is followed by an accumulator

and 16-bit input port which allows the user to cascade multi-

ple TMC2249As. A new 16-bit accumulated output is avail-

able every clock, up to the maximum rate of 60 MHz. All

inputs and outputs are registered except the three-state out-

put enable, and all are TTL compatible.

Logic Symbol

TMC2249A

Digital Mixer

CLK

NEG1

NEG2

SWAP

OE

ACC

RND

FT

CASEN

S

15-0

Delay

1-16

Delay

1-16

Delay

1-16

Delay

1-16

B

11-0

ADEL

3-0

ENA

A

11-0

BDEL

3-0

ENB

C

11-0

CDEL

3-0

ENC

D

11-0

DDEL

3-0

END

CAB

15-0

The TMC2249A utilizes a pipelined, bus-oriented structure

offering significant flexibility. Input register clock enables

and programmable input data pipeline delays on each port

offer an adaptable input structure for high-speed digital

systems. Following the multipliers, the user may perform

addition or subtraction of either product, arithmetic rounding

to 16 bits, and accumulation and summation of products with a

cascading input. The output port allows access to all 24 bits of

the internal accumulator by switching between overlapping

least and most-significant 16-bit words, and a three-state out-

put enable simplifies connection to an external system bus.

The TMC2249A has numerous applications in digital pro-

cessing algorithms, from executing simple image mixing and

switching, to performing complex arithmetic functions and

complex waveform synthesis. FIR filters, digital quadrature

mixers and modulators, and vector arithmetic functions may

also be implemented with this device.

Fabricated in a submicron CMOS process, the TMC2249A

operates at guaranteed clock rates of up to 60 MHz over the

full temperature and supply voltage ranges. It is pin- and

function-compatible with Fairchild’s TMC2249, while pro-

viding higher speed operation and lower power dissipation. It

is available in a 120 pin Ceramic Pin Grid Array (CPGA),

120 pin Plastic Pin Grid Array (PPGA), 120 lead MQFP to

PPGA package (MPGA), and a 120 lead Metric Quad Flat-

Pack (MQFP).

T MC2249A

Digital Mixer

12 x 12 Bit, 60 MHz

相關PDF資料 |

PDF描述 |

|---|---|

| TMC2249AH5C | Digital Mixer 12 x 12 Bit, 60 MHz |

| TMC2249AH5C1 | Digital Mixer 12 x 12 Bit, 60 MHz |

| TMC2249AH5C2 | Digital Mixer 12 x 12 Bit, 60 MHz |

| TMC2250AH5C | Matrix Multiplier 12 x 10 bit, 50 MHz |

| TMC2250AH5C2 | Matrix Multiplier 12 x 10 bit, 50 MHz |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TMC2250/TMC2272 WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| TMC2250A | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Matrix Multiplier 12 x 10 bit, 50 MHz |

| TMC2250AG1C | 制造商:CADEKA 制造商全稱:CADEKA 功能描述:Matrix Multiplier 12 x 10 bit, 50 MHz |

| TMC2250AG1C2 | 制造商:CADEKA 制造商全稱:CADEKA 功能描述:Matrix Multiplier 12 x 10 bit, 50 MHz |

| TMC2250AG1C3 | 制造商:CADEKA 制造商全稱:CADEKA 功能描述:Matrix Multiplier 12 x 10 bit, 50 MHz |

發布緊急采購,3分鐘左右您將得到回復。