- 您現在的位置:買賣IC網 > PDF目錄382647 > TMX320C6202BGGP167 (Texas Instruments, Inc.) Aluminum Electrolytic Radial Lead Low Impedance Capacitor; Capacitance: 470uF; Voltage: 16V; Case Size: 10x12.5 mm; Packaging: Bulk PDF資料下載

參數資料

| 型號: | TMX320C6202BGGP167 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Aluminum Electrolytic Radial Lead Low Impedance Capacitor; Capacitance: 470uF; Voltage: 16V; Case Size: 10x12.5 mm; Packaging: Bulk |

| 中文描述: | 定點數字信號處理器 |

| 文件頁數: | 76/83頁 |

| 文件大小: | 1176K |

| 代理商: | TMX320C6202BGGP167 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁當前第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁

TMS320C6211, TMS320C6211B

FIXED-POINT DIGITAL SIGNAL PROCESSORS

SPRS073K

AUGUST 1998

REVISED MARCH 2004

76

POST OFFICE BOX 1443

HOUSTON, TEXAS 77251

1443

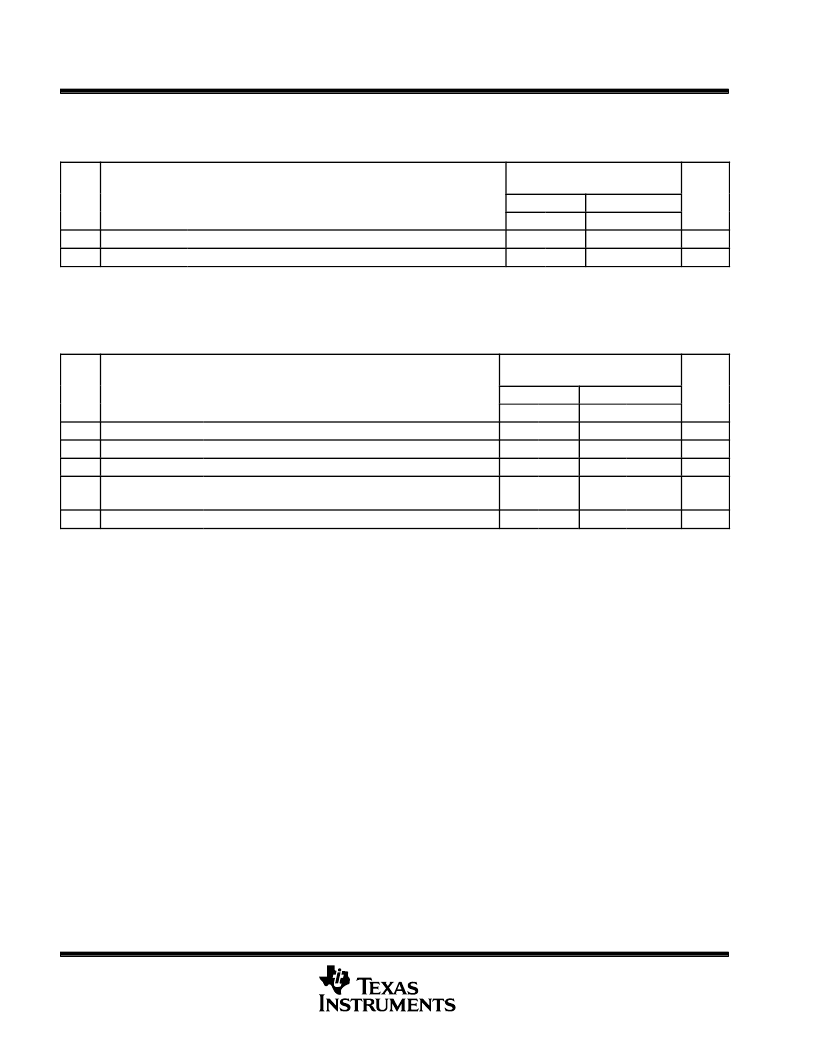

MULTICHANNEL BUFFERED SERIAL PORT TIMING (CONTINUED)

timing requirements for McBSP as SPI master or slave: CLKSTP = 11b, CLKXP = 1

(see Figure 42)

NO.

150

167

UNIT

MASTER

MIN

26

4

SLAVE

MIN

2

6P

6 + 12P

MAX

MAX

4

5

t

su(DRV-CKXH)

t

h(CKXH-DRV)

Setup time, DR valid before CLKX high

Hold time, DR valid after CLKX high

ns

ns

P = 1/CPU clock frequency in ns. For example, when running parts at 167 MHz, use P = 6 ns.

For all SPI slave modes, CLKG is programmed as 1/2 of the CPU clock by setting CLKSM = CLKGDV = 1.

switching characteristics over recommended operating conditions for McBSP as SPI master or

slave: CLKSTP = 11b, CLKXP = 1

(see Figure 42)

NO.

PARAMETER

150

167

UNIT

MASTER

§

MIN

H

9

T

9

9

SLAVE

MIN

MAX

H + 9

T + 9

MAX

1

2

3

t

h(CKXH-FXL)

t

d(FXL-CKXL)

t

d(CKXH-DXV)

Hold time, FSX low after CLKX high

Delay time, FSX low to CLKX low

#

Delay time, CLKX high to DX valid

Disable time, DX high impedance following last data bit from

CLKX high

ns

ns

ns

9

6P + 4

10P + 20

6

t

dis(CKXH-DXHZ)

9

9

6P + 3

10P + 20

ns

7

t

d(FXL-DXV)

Delay time, FSX low to DX valid

L

9

L + 9

4P + 2

8P + 20

ns

P = 1/CPU clock frequency in ns. For example, when running parts at 167 MHz, use P = 6 ns.

For all SPI slave modes, CLKG is programmed as 1/2 of the CPU clock by setting CLKSM = CLKGDV = 1.

§

S =

Sample rate generator input clock = 2P if CLKSM = 1 (P = 1/CPU clock frequency)

=

Sample rate generator input clock = P_clks if CLKSM = 0 (P_clks = CLKS period)

T =

CLKX period = (1 + CLKGDV) * S

H =

CLKX high pulse width = (CLKGDV/2 + 1) * S if CLKGDV is even

= (CLKGDV + 1)/2 * S if CLKGDV is odd or zero

L =

CLKX low pulse width

= (CLKGDV/2) * S if CLKGDV is even

= (CLKGDV + 1)/2 * S if CLKGDV is odd or zero

FSRP = FSXP = 1. As a SPI master, FSX is inverted to provide active-low slave-enable output. As a slave, the active-low signal input on FSX

and FSR is inverted before being used internally.

CLKXM = FSXM = 1, CLKRM = FSRM = 0 for master McBSP

CLKXM = CLKRM = FSXM = FSRM = 0 for slave McBSP

#

FSX should be low before the rising edge of clock to enable slave devices and then begin a SPI transfer at the rising edge of the master clock

(CLKX).

相關PDF資料 |

PDF描述 |

|---|---|

| TMX320C6203BGGP167 | Aluminum Electrolytic Radial Lead High Ripple High Reliability Capacitor; Capacitance: 1000uF; Voltage: 10V; Case Size: 10x16 mm; Packaging: Bulk |

| TMX320C6211BGGP167 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMP320C6202BGGP167 | Aluminum Electrolytic Radial Lead High Ripple High Reliability Capacitor; Capacitance: 1000uF; Voltage: 16V; Case Size: 10x20 mm; Packaging: Bulk |

| TMX320C6202GLW167 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMX320C6211GLZ167 | FIXED-POINT DIGITAL SIGNAL PROCESSORS |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TMX320C6202BGHK100 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSOR |

| TMX320C6202BGHK167 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMX320C6202BGJC100 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSOR |

| TMX320C6202BGJC167 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSORS |

| TMX320C6202BGJL100 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:FIXED-POINT DIGITAL SIGNAL PROCESSOR |

發布緊急采購,3分鐘左右您將得到回復。