- 您現在的位置:買賣IC網 > PDF目錄382672 > TP3056B (Texas Instruments, Inc.) MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER PDF資料下載

參數資料

| 型號: | TP3056B |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | Codec |

| 英文描述: | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| 中文描述: | 整體式串行接口的PCM編解碼器和過濾器 |

| 文件頁數: | 10/19頁 |

| 文件大小: | 287K |

| 代理商: | TP3056B |

TP3056B

MONOLITHIC SERIAL INTERFACE

COMBINED PCMCODEC AND FILTER

SLWS072A – MAY 1998 – REVISED AUGUST 1998

10

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

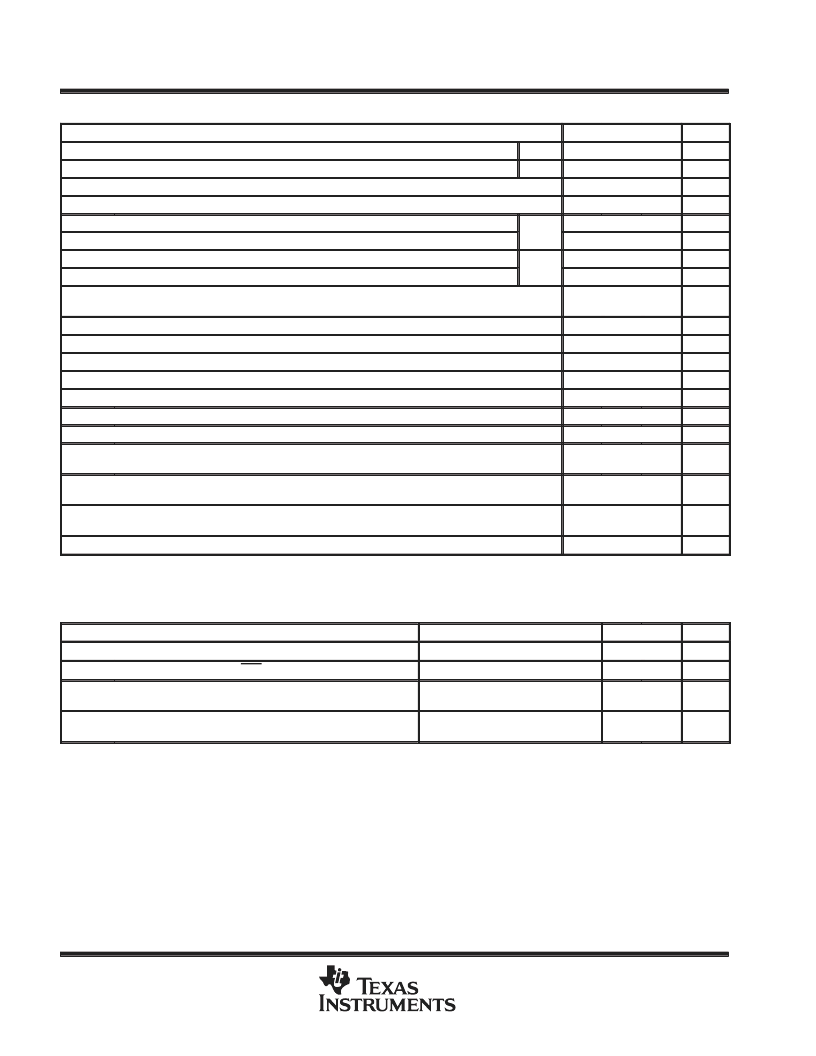

timing requirements over recommended ranges of operating conditions (see Figures 1 and 2)

MIN

NOM

MAX

UNIT

fclock(M)

fclock(B)

tw1

tw2

tr1

tf1

tr2

tf2

Frequency of master clock

MCLK

2.048

MHz

Frequency of bit clock, transmit

BCLK

64

2048

kHz

Pulse duration, MCLK high

160

ns

Pulse duration, MCLK low

160

ns

Rise time of master clock (20% to 80%)

MCLK

50

ns

Fall time of master clock (80% to 20%)

50

ns

Rise time of bit clock (20% to 80%), transmit

BCLK

50

ns

Fall time of bit clock (80% to 20%), transmit

Setup time, BCLK high (and FSX in long-frame sync mode) before MCLK

↓

(first bit clock after

the leading edge of FSX)

50

ns

tsu1

100

ns

tw3

tw4

th1

th2

tsu2

tsu3

th3

Pulse duration, BCLK high, VIH = 2.2 V

Pulse duration, BCLK low, VIL = 0.6 V

Hold time, FSX or FSR low after BCLK low (long frame only)

Hold time, BCLK high after FSX or FSR

↑

(short frame only)

Setup time, FSX or FSR high before BCLK

↓

(long frame only)

Setup time, DR valid before BCLK

↓

Hold time, DR valid after BCLK

↓

Setup time, FSX or FSR high before BCLK

↓

, short-frame sync pulse (1 or 2

bit-clock periods long) (see Note 7)

Hold time, FSX or FSR high after BCLK

↓

, short-frame sync pulse (1 or 2

bit-clock periods long) (see Note 7)

Hold time, FSX or FSR high after BCLK

↓

, long-frame sync pulse (from 3 to 8 bit-clock periods

long)

160

ns

160

ns

0

ns

0

ns

80

ns

50

ns

50

ns

tsu4

50

ns

th4

100

ns

th5

100

ns

tw5

NOTE 7: For short-frame sync timing, FSR and FSX must go high while their respective bit clocks are high.

Minimum pulse duration of FSX or FSR (frame sync pulse — low level), 64-kbps operating mode

160

ns

switching characteristics over recommended ranges of operating conditions (see Figures 1

and 2)

PARAMETER

TEST CONDITIONS

Load = 150 pF plus 2 LSTTL loads

Load = 150 pF plus 2 LSTTL loads

MIN

MAX

UNIT

td1

td2

Delay time, BCLK high to data valid at DX

0

140

ns

Delay time, BCLK high to TSX low

140

ns

td3

Delay time, BCLK (or 8 clock FSX in long frame only) low to

data output (DX) disabled

50

165

ns

td4

Delay time, FSX or BCLK high to data valid at DX (long frame

only)

Nominal input value for an LSTTL load is 18 k

.

CL = 0 pF to 150 pF

20

165

ns

相關PDF資料 |

PDF描述 |

|---|---|

| TP3056BDW | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| TP3056BN | MONOLITHIC SERIAL INTERFACE COMBINED PCM CODEC AND FILTER |

| TP3098 | TRANSISTOR | BJT | NPN | 200MA I(C) | RFMOD |

| TP3102 | 1 Cell Li-ion Battery Protection + Cell Pack |

| TP3330N | MODEM |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TP3056BDW | 功能描述:接口—CODEC PCM CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TP3056BDWR | 功能描述:接口—CODEC Mono Serial Intfc PCM Codec/Filter RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TP3056BN | 功能描述:接口—CODEC PCM CODEC RoHS:否 制造商:Texas Instruments 類型: 分辨率: 轉換速率:48 kSPs 接口類型:I2C ADC 數量:2 DAC 數量:4 工作電源電壓:1.8 V, 2.1 V, 2.3 V to 5.5 V 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:DSBGA-81 封裝:Reel |

| TP3056J | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:PARALLEL INTERFACE CODEC/FILTER COMBO |

| TP3056V | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:A-Law CODEC |

發布緊急采購,3分鐘左右您將得到回復。