- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄382678 > TPS31XXK33 (Texas Instruments, Inc.) ULTRALOW SUPPLY-CURRENT/SUPPLY-VOLTAGE SUPERVISORY CIRCUITS PDF資料下載

參數(shù)資料

| 型號: | TPS31XXK33 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | ULTRALOW SUPPLY-CURRENT/SUPPLY-VOLTAGE SUPERVISORY CIRCUITS |

| 中文描述: | 超低SUPPLY-CURRENT/SUPPLY-VOLTAGE監(jiān)控電路 |

| 文件頁數(shù): | 12/19頁 |

| 文件大小: | 306K |

| 代理商: | TPS31XXK33 |

TPS31xxExx, TPS31xxH20, TPS31xxK33

ULTRALOW SUPPLY-CURRENT/SUPPLY-VOLTAGE SUPERVISORY CIRCUITS

SLVS363

–

AUGUST 2001

12

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

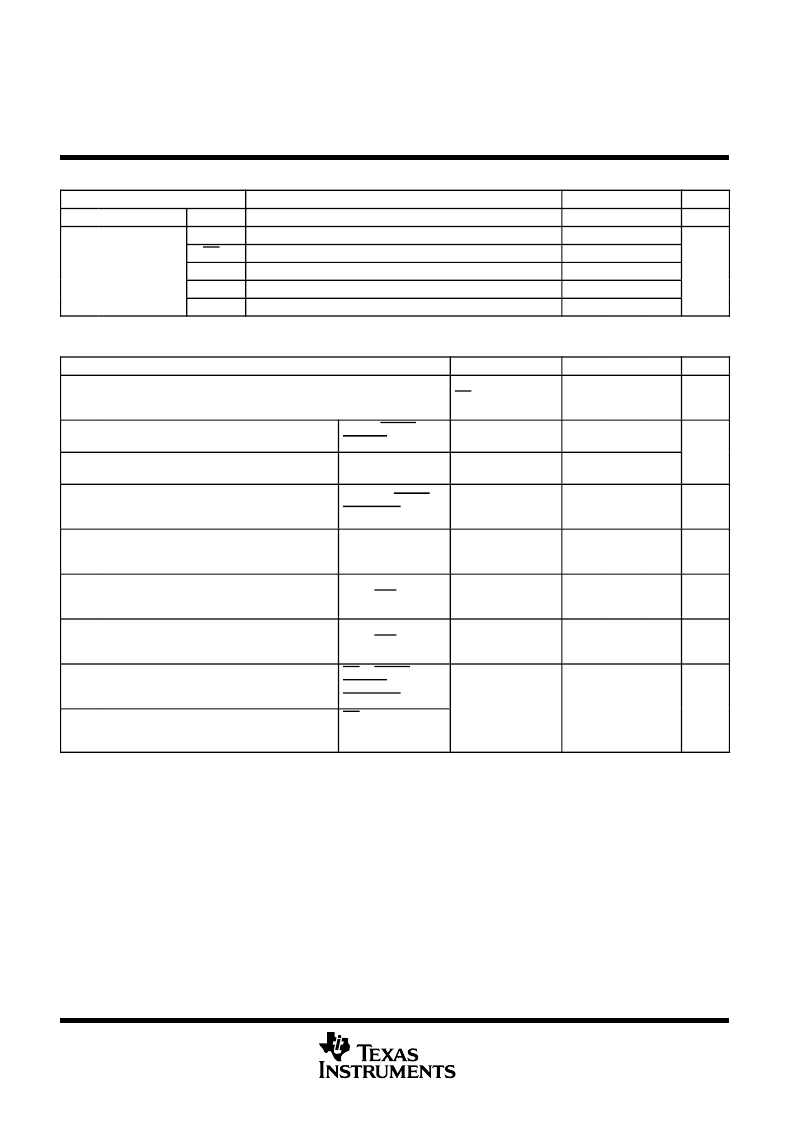

timing requirements at R

L

= 1 M

, C

L

= 50 pF, T

A

=

–

40

°

C to 85

°

C

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

tt(out)

Time-out period

at WDI

VDD

≥

0.85 V

VIH = 1.1

×

VIT, VIL = 0.9

×

VIT

–

, VIT

–

= 0.86 V

VDD

≥

VIT + 0.2 V, VIL = 0.3

×

VDD,

VDD

≥

VIT,

VIH = 1.1

×

VIT

–

(S), VIL = 0.9

×

VIT

–

(S)

VDD

≥

0.85 V,

VIH = 1.1

×

VIT

–

(S),VIL = 0.9

×

VIT

–

(S)

VDD

≥

VIT,

VIL = 0.3

×

VDD,

0.55

1.1

1.65

s

at VDD

at MR

20

VIH = 0.7

×

VDD

0.1

tw

Pulse width

at SENSE

20

s

μ

at PFI

20

at WDI

VIH = 0.7

×

VDD

0.3

switching characteristics at R

L

= 1 M

, C

L

= 50 pF, T

A

=

–

40

°

C to 85

°

C

PARAMETER

TEST CONDITIONS

VDD

≥

1.1

×

VIT,

MR = 0.7

×

VDD,

See timing diagram

VIH = 1.1

×

VIT,

VIL = 0.9

×

VIT

VIH = 1.1

×

VIT,

VIL = 0.9

×

VIT

VDD

≥

0.8 V,

VIH = 1.1

×

VIT,

VIL = 0.9

×

VIT

VDD

≥

0.8 V,

VIH = 1.1

×

VIT,

VIL = 0.9

×

VIT

VDD

≥

0.8 V,

VIH = 1.1

×

VIT,

VIL = 0.9

×

VIT

VDD

≥

0.8 V,

VIH = 1.1

×

VIT,

VIL = 0.9

×

VIT

MIN

TYP

MAX

UNIT

td

Delay time

65

130

195

ms

tPHL

Propagation delay time, high-to-low level output

VDD to RESET or

RSTVDD delay

40

tPLH

Propagation delay time, low-to-high level output

VDD to RESET or

RSTVDD delay

40

μ

s

tPHL

Propagation delay time, high-to-low level output

SENSE to RESET or

RSTSENSE delay

40

μ

s

tPLH

Propagation delay time, high-to-low level output

SENSE to RESET or

RSTSENSE delay

40

μ

s

tPHL

Propagation delay time, high-to-low level output

PFI to PFO delay

40

μ

s

tPLH

Propagation delay time, low-to-high level output

PFI to PFO delay

300

μ

s

tPHL

Propagation delay time, low-to-high level output

MR to RESET.

RSTVDD,

RSTSENSE delay

VDD

≥

1.1

×

VIT,

0 3

×

VIL = 0.3

VDD,

VIH = 0.7

×

VDD

1

5

tPLH

Propagation delay time, low-to-high level output

MR to RESET.

RSTVDD,

RSTSENSE delay

μ

s

相關PDF資料 |

PDF描述 |

|---|---|

| TPS3513 | 3-Channel Supervisor With Over-Current Detect For Switch-Mode Power Supplies |

| TPS3513D | Analog IC |

| TPS3513N | Analog IC |

| TPS3809I50DBV | 3-PIN SUPPLY VOLTAGE SUPERVISORS |

| TPS3809J25DBV | 3-PIN SUPPLY VOLTAGE SUPERVISORS |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| TPS320DA150GGU120 | 制造商:Texas Instruments 功能描述: |

| TPS3305 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DUAL PROCESSOR SUPERVISORS |

| TPS3305- | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DUAL PROCESSOR SUPERVISORS |

| TPS3305-18 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:雙處理器監(jiān)事 |

| TPS3305-18/3305-25/3305-33 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Dual Processor Supervisors |

發(fā)布緊急采購,3分鐘左右您將得到回復。