- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98286 > TPS65930BZCHR (TEXAS INSTRUMENTS INC) SPECIALTY CONSUMER CIRCUIT, PBGA139 PDF資料下載

參數(shù)資料

| 型號: | TPS65930BZCHR |

| 廠商: | TEXAS INSTRUMENTS INC |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PBGA139 |

| 封裝: | 10 X 10 MM, 0.65 MM PITCH, GREEN, PLASTIC, NFBGA-139 |

| 文件頁數(shù): | 87/115頁 |

| 文件大小: | 1232K |

| 代理商: | TPS65930BZCHR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁當(dāng)前第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁

UART_TX

DM

DP

UART_RX

CK1

CK2

CK3

CK4

037-047

SWCS037G

– MAY 2008 – REVISED APRIL 2011

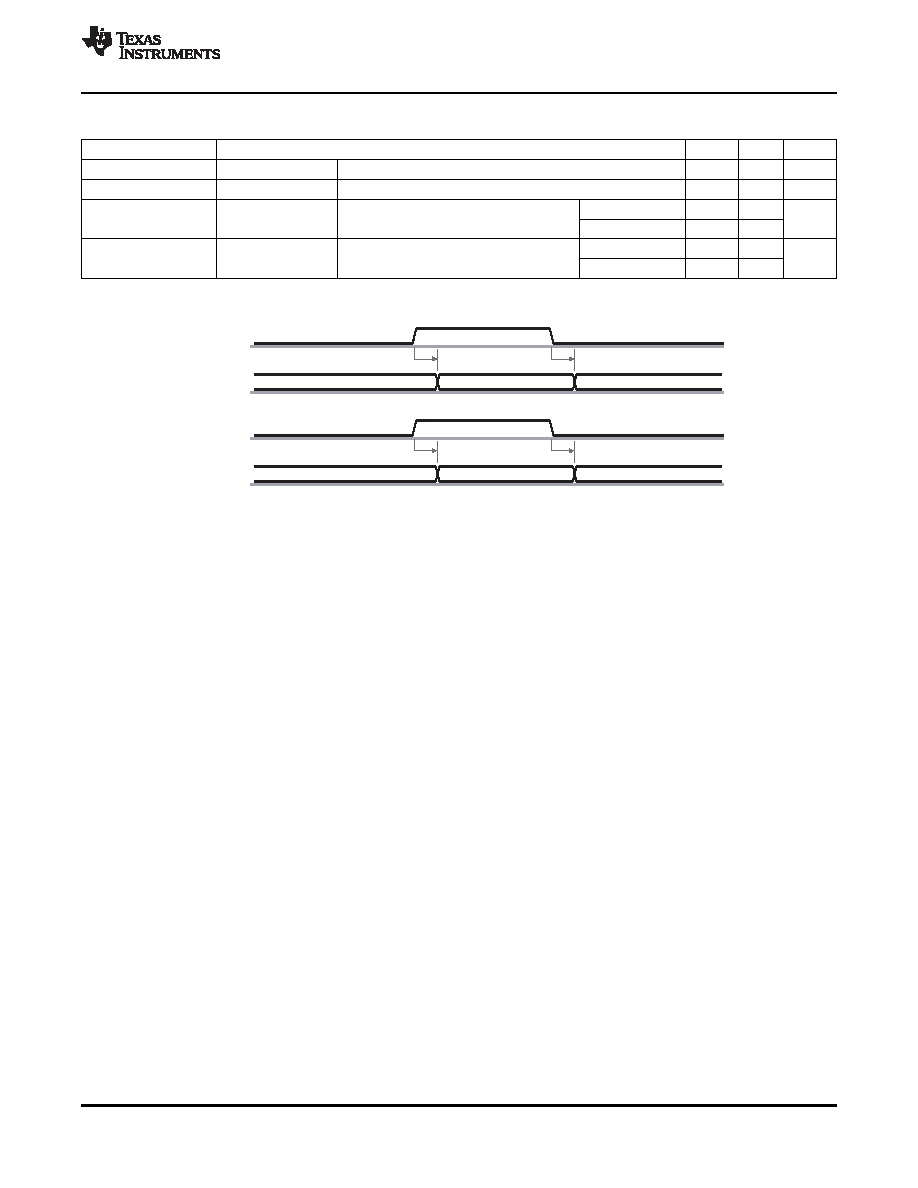

Table 7-4. USB-CEA Carkit UART Timings

Notation

Parameter

Min

Max

Unit

CK1

td(UART_TXH-DM)

Delay time, UART_TX rising edge to DM transition

4.0

11

ns

CK2

td(UART_TXL-DM)

Delay time, UART_TX falling edge to DM transition

4.0

11

ns

At 38.4 MHz

205

234

Delay time, DP rising edge to UART_RX

CK3

td(DPH-UART_RX)

ns

transition

At 19.2 MHz

310

364

At 38.4 MHz

205

234

Delay time, DP falling edge to UART_RX

CK4

td(DPL-UART_RX)

ns

transition

At 19.2 MHz

310

364

Figure 7-5 shows the USB-CEA carkit UART timings.

Figure 7-5. USB-CEA Carkit UART Timings

7.1.4

PHY Electrical Characteristics

The PHY is the physical signaling layer of the USB 2.0. It contains the drivers and receivers for physical

data and protocol signaling on the DP and DM lines.

The PHY interfaces with the USB controller through the UTMI.

The transmitters and receivers in the PHY are of two main classes:

FS and LS transceivers (legacy USB1.x transceivers)

HS transceivers

To bias the transistors and run the logic, the PHY also contains reference generation circuitry which

consists of:

A DPLL that does a frequency multiplication to achieve the 480-MHz low-jitter lock necessary for USB,

and the clock required for the switched capacitor resistance block

A switched capacitor resistance block that replicates an external resistor on chip

Built-in pullup and pulldown resistors are used as part of the protocol signaling.

The PHY also contains circuitry that protects it from an accidental 5-V short on the DP and DM lines and

from 8-kV IEC ESD strikes.

7.1.4.1

HS Differential Receiver

The HS receiver consists of the following blocks:

A differential input comparator to receive the serial data

A squelch detector to qualify the received data

An oversampler-based clock data recovery scheme followed by a nonreturn to zero inverted (NRZI)

decoder, bit unstuffing, and serial-to-parallel converter to generate the UTMI DATAOUT

Table 7-5 lists the characteristics of the HS differential receiver.

Copyright

2008–2011, Texas Instruments Incorporated

USB Transceiver

73

focus.ti.com: TPS65930/TPS65920

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| TPS65930BZCH | SPECIALTY CONSUMER CIRCUIT, PBGA139 |

| TPS65950ZXNR | SPECIALTY CONSUMER CIRCUIT, PBGA209 |

| TPS65950ZXNT | SPECIALTY CONSUMER CIRCUIT, PBGA209 |

| TPS6735Y | 2 A SWITCHING REGULATOR, 160 kHz SWITCHING FREQ-MAX, UUC12 |

| TPS6735IP | 2 A SWITCHING REGULATOR, 160 kHz SWITCHING FREQ-MAX, PDIP8 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| TPS65950A2ZXN | 功能描述:PMIC 解決方案 Integ Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

| TPS65950A2ZXNR | 功能描述:PMIC 解決方案 Integ Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

| TPS65950A3ZXN | 功能描述:PMIC 解決方案 Integrated Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

| TPS65950A3ZXNR | 功能描述:PMIC 解決方案 Integrated Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-24 封裝:Reel |

| TPS65950BZXN | 功能描述:開關(guān)變換器、穩(wěn)壓器與控制器 Integ Pwr Mgmt IC RoHS:否 制造商:Texas Instruments 輸出電壓:1.2 V to 10 V 輸出電流:300 mA 輸出功率: 輸入電壓:3 V to 17 V 開關(guān)頻率:1 MHz 工作溫度范圍: 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:WSON-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。