- 您現在的位置:買賣IC網 > PDF目錄98299 > TS8388BCFS9NB2ZB9 (ATMEL CORP) 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 PDF資料下載

參數資料

| 型號: | TS8388BCFS9NB2ZB9 |

| 廠商: | ATMEL CORP |

| 元件分類: | ADC |

| 英文描述: | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| 封裝: | CERAMIC, QFP-68 |

| 文件頁數: | 39/43頁 |

| 文件大小: | 825K |

| 代理商: | TS8388BCFS9NB2ZB9 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁當前第39頁第40頁第41頁第42頁第43頁

TS8388BFS

5/42

Preliminary Beta Site

3.3.

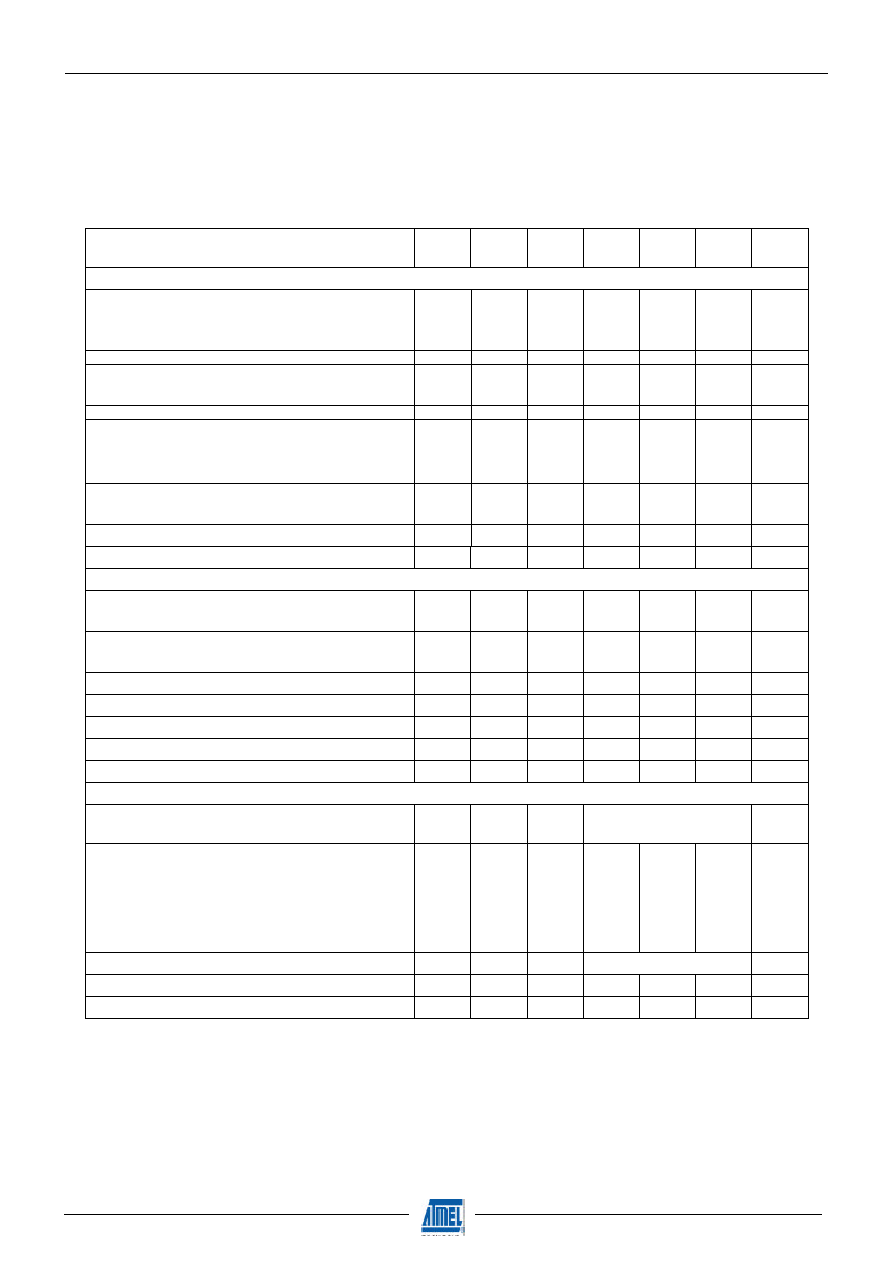

ELECTRICAL OPERATING CHARACTERISTICS

VEE = DVEE = -5 V ; VCC = +5 V ; VIN -VINB = 500 mVpp Full Scale differential input ;

Digital outputs 75 or 50

differentially terminated ;

Tj (typical) = 70

°C. Full temperature range : -55°C < Tc ; Tj < +125°C

Parameter

Symb

Temp

Test

level

Min

Typ

Max

Unit

POWER REQUIREMENTS

Positive supply voltage

Analog

Digital (ECL)

Digital (LVDS)

VCC

VPLUSD

II,IV

4.75

1.4

5

0

2.4

5.25

2.6

V

Positive supply current

Analog

Digital

ICC

IPLUSD

II, IV

400

120

425

130

mA

Negative supply voltage

VEE

Full

IV

-5.25

-5

-4.75

V

Negative supply current

Analog

Digital

AIEE

DIEE

II,IV

170

140

185

160

mA

Nominal power dissipation

PD

Full

II

IV

3.6

3.8

3.7

3.9

W

Power supply rejection ratio

(note 2)

PSRR

IV

+/- 0.5

mV/V

RESOLUTION

8

bits

ANALOG INPUTS

Full Scale Input Voltage range (differential mode)

( 0 Volt common mode voltage )

VIN

VINB

Full

IV

-125

125

mV

Full Scale Input Voltage range (single–ended input option )

(see Application Notes)

VIN

VINB

Full

IV

-250

0

250

mV

Analog input capacitance

CIN

Full

IV

3

3.5

pF

Input bias current

IIN

Full

IV

10

20

A

Input Resistance

RIN

Full

IV

0.5

1

M

Full Power input Bandwidth

FPBW

Full

IV

1.3

1.5

GHz

Small Signal input Bandwidth (10 % full scale)

SSBW

Full

IV

1.5

1.7

GHz

CLOCK INPUTS

Logic compatibility for clock inputs

(note 10 )

(see Application Notes)

ECL or specified clock input

power level in dBm

ECL Clock inputs voltages (VCLK or VCLKB) :

Full

IV

Logic “0” voltage

VIL

-1.5

V

Logic “1” voltage

VIH

-1.1

V

Logic “0” current

IIL

5

A

Logic “1” current

IIH

5

A

Clock input power level into 50

termination

DBm into 50

Clock input power level

Full

IV

-2

4

10

dBm

Clock input capacitance

CCLK

Full

IV

3

3.5

pF

相關PDF資料 |

PDF描述 |

|---|---|

| TS8388BVFS9QC1ZB9 | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| TS8388BCFS9QB1ZB9 | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| TS8388BVFS9NC3ZB9 | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| TS8388BVFS9QC1ZB9 | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

| TS8388BCFS9QB3ZB9 | 1-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, CQFP68 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| TS8388BCG | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:A/D CONVERTER |

| TS8388BCGL | 制造商:e2v technologies 功能描述:ADC 8-BIT 1 GSPS - Trays |

| TS8388BCGL (+LID) | 制造商:e2v technologies 功能描述:ADC 8-BIT 1 GSPS - Trays |

| TS8388BMF | 制造商:e2v technologies 功能描述:ADC 8-BIT 1 GSPS - Trays |

| TS8388BMFB/Q | 制造商:e2v technologies 功能描述:ADC 8-BIT 1 GSPS - Trays |

發布緊急采購,3分鐘左右您將得到回復。