- 您現在的位置:買賣IC網 > PDF目錄382718 > UC2633Q Analog Phase-Locked Loop PDF資料下載

參數資料

| 型號: | UC2633Q |

| 英文描述: | Analog Phase-Locked Loop |

| 中文描述: | 模擬鎖相環 |

| 文件頁數: | 5/8頁 |

| 文件大小: | 588K |

| 代理商: | UC2633Q |

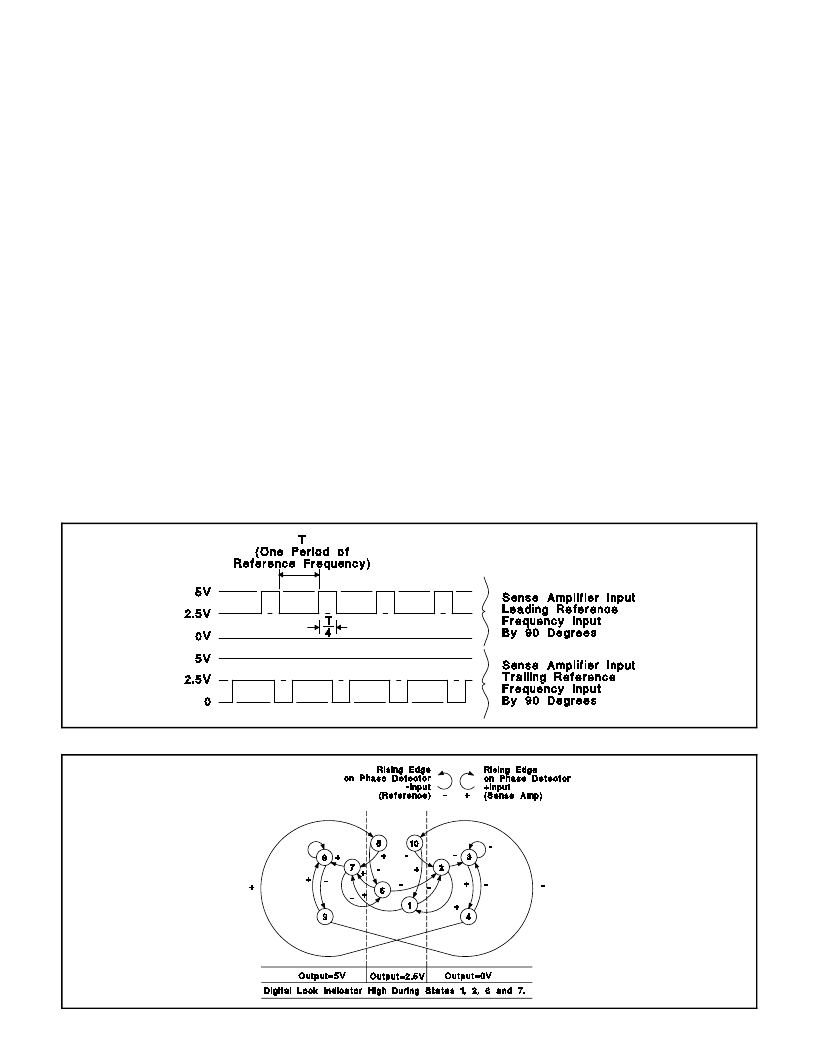

Phase Detector Operation

The phase detector on these devices is a digital circuit

that responds to the rising edges of the detector’s two in-

puts. The phase detector output has three states: a high,

5V state, a low, 0V state, and a middle, 2.5V state. In the

high and low states the output impedance of the detector

is low and the middle state output impedence is high, typi-

cally 6.0k

. When there is any static frequency difference

between the inputs, the detector output is fixed at its high

level if the +input (the sense amplifier signal) is greater in

frequency, and fixed at its low level if the -input (the refer-

ence frequency signal) is greater in frequency.

When the frequencies of the two inputs to the detector

are equal, the phase detector switches between its middle

state and either the high or low states, depending on the

relative phase of the two signals. If the +input is leading in

phase then, during each period of the input frequency, the

detector output will be high for a time equal to the time dif-

ference between the rising edges of the inputs, and will

be at its middle level for the remainder of the period. If the

phase relationship is reversed, then the detector will go

low for a time proportional to the phase difference of the

inputs. The resulting gain of the phase detector. k, is

5V/4

π

radians or about 0.4V/radian. The dynamic range of

the detector is

±

2

π

radians.

The operation of the phase detector is illustrated in the

figures below. The upper figure shows typical voltage

waveforms seen at the detector output for leading and

lagging phase conditions. The lower figure is a state dia-

gram of the phase detector logic. In this figure, the circles

represent the 10 possible states of the logic, and the con-

necting arrows represent the transition events/paths to

and from these states. Transition arrows that have a clock-

wise rotation are the result of a rising edge on the +input,

and conversely, those with counter-clockwise rotation are

tied to the rising edge of the -input signal.

The normal operational states of the logic are 6 and 7 for

positive phase error, 1 and 2 for a negative phase error.

States 8 and 9 occur during positive frequency error, 3

and 4 during negative frequency error. States 5 and 10

occur only as the inputs cross over from the frequency er-

ror to a normal phase error only condition. The level of the

phase detector output is determined by the logic state as

defined in the state diagram figure. The lock indicator out-

put is high, off, when the detector is in states 1, 2, 6, or 7.

UC1633

UC2633

UC3633

Typical Phase Detector Output Waveforms

Phase Detector State Diagram

APPLICATION AND OPERATION INFORMATION

5

Powered by ICminer.com Electronic-Library Service CopyRight 2003

相關PDF資料 |

PDF描述 |

|---|---|

| UC2633QTR | Iso high side smart power solid state relay |

| UC3633J | DMOS driver for bipolar stepper motor |

| UC3633Q | Analog Phase-Locked Loop |

| UC3633QTR | Stepper motor driver |

| UC2727J | Single channel high side driver |

相關代理商/技術參數 |

參數描述 |

|---|---|

| UC2633QTR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog Phase-Locked Loop |

| UC2634 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:Phase Locked Frequency Controller |

| UC2634 WAF | 制造商:Texas Instruments 功能描述: |

| UC2634DW | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog Phase-Locked Loop |

| UC2634DWTR | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Analog Phase-Locked Loop |

發布緊急采購,3分鐘左右您將得到回復。