- 您現在的位置:買賣IC網 > PDF目錄382720 > UDA1331H (NXP SEMICONDUCTORS) Universal Serial Bus USB Audio Playback Peripheral APP PDF資料下載

參數資料

| 型號: | UDA1331H |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費家電 |

| 英文描述: | Universal Serial Bus USB Audio Playback Peripheral APP |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP64 |

| 封裝: | 14 X 20 MM, 2.80 MM HEIGHT, PLASTIC, SOT-319-2, QFP-64 |

| 文件頁數: | 9/40頁 |

| 文件大小: | 181K |

| 代理商: | UDA1331H |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

1998 Oct 06

9

Philips Semiconductors

Preliminary specification

Universal Serial Bus (USB) Audio

Playback Peripheral (APP)

UDA1331H

The Asynchronous Digital-to-Analog Converter

(ADAC)

The ADAC receives USB audio information from the USB

processor or from the digital I/O-bus. The ADAC is able to

reconstruct the sample clock from the rate at which the

audio samples arrive and handles the audio sound

processing. After processing, the audio signal is

up-sampled, noise-shaped and converted to analog output

voltages capable of driving a line output. The ADAC

consists of:

A Sample Frequency Generator (SFG)

First-In First-Out (FIFO) registers

An audio feature processing DSP

Two digital up-sample filters

A variable hold register

A digital Noise Shaper (NS)

A Filter Stream DAC (FSDAC) with integrated filter and

line output drivers.

T

HE

S

AMPLE

F

REQUENCY

G

ENERATOR

(SFG)

The SFG controls the timing signals for the asynchronous

digital-to-analog conversion. By means of a digital PLL,

the SFG automatically recovers the applied sampling

frequency and generates the accurate timing signals for

the audio feature processing DSP and the up-sample

filters.

F

IRST

-I

N

F

IRST

-O

UT

(FIFO)

REGISTERS

The FIFO registers are used to store the audio samples

temporarily coming from the USB processor or from the

digital I/O input. The use of a FIFO register (in conjunction

with the SFG) is necessary to remove all jitter present on

the incoming audio signal.

T

HE AUDIO FEATURE PROCESSING

DSP

A DSP processes the sound features. The control and

mapping of the sound features is explained in Section

“Controlling the USB Audio Playback Peripheral (APP)”.

Depending on the sampling rate (f

s

) the DSP has four

frequency domains in which the treble and bass are

regulated (see Table 1). The domain is chosen

automatically.

T

HE UP

-

SAMPLE FILTERS AND VARIABLE HOLD REGISTER

After the audio feature processing DSP two up-sample

filters and a variable hold register increase the

oversampling rate to 128f

s

.

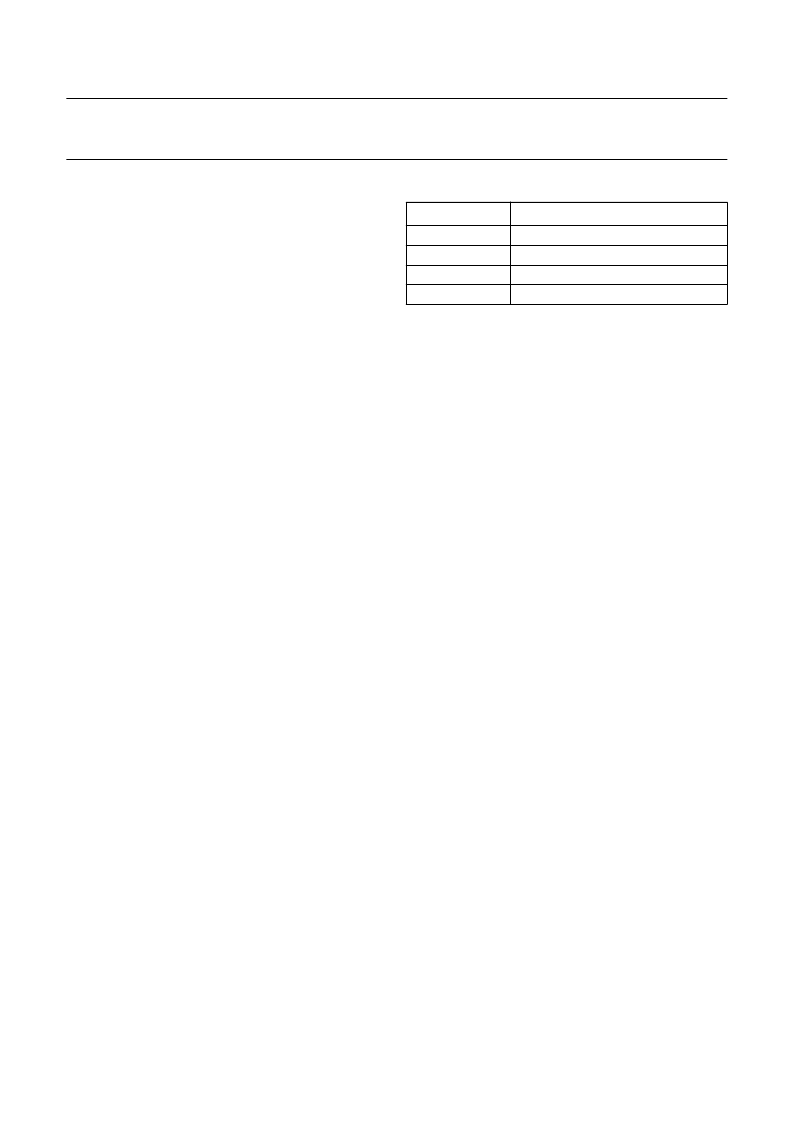

Table 1

Frequency domains for audio processing

T

HE NOISE SHAPER

A 3rd-order noise shaper converts the oversampled data

to a noise-shaped bitstream for the FSDAC. The in-band

quantization noise is shifted to frequencies well above the

audio band.

T

HE

F

ILTER

S

TREAM

DAC (FSDAC)

The FSDAC is a semi-digital reconstruction filter that

converts the 1-bit data stream of the noise shaper to an

analog output voltage. The filter coefficients are

implemented as current sources and are summed at

virtual ground of the output operational amplifier. In this

way very high signal-to-noise performance and low clock

jitter sensitivity is achieved. A post filter is not needed

because of the inherent filter function of the DAC.

On-board amplifiers convert the FSDAC output current to

an output voltage signal capable of driving a line output.

USB Audio Playback Peripheral (APP) descriptors

In a typical USB environment the USB host has to know

which kind of devices are connected. For this purpose

each device contains a number of USB descriptors. These

descriptors describe, from different points of view (USB

configuration, USB interface and USB endpoint), the

capabilities of a device. Each of them can be requested by

the host. The collection of descriptors is denoted as a

descriptor map. This descriptor map will be reported to the

USB host during enumeration and on request.

The full descriptor map is implemented in the firmware

exploiting the full functionality of the UDA1331H. The USB

descriptors and their most important fields, in relationship

to the characteristics of the UDA1331H are briefly

explained below.

G

ENERAL DESCRIPTORS

The UDA1331H supports one configuration containing a

control interface, an audio interface and a HID interface.

The descriptor map that describes this configuration is

partly fixed and partly programmable.

DOMAIN

SAMPLE FREQUENCY (kHz)

1

2

3

4

5 to 12

12 to 25

25 to 40

40 to 55

相關PDF資料 |

PDF描述 |

|---|---|

| UDA1334BT | Low power audio DAC |

| UDA1334TS | Low power audio DAC |

| UDA1335H | Universal Serial Bus USB Audio Playback Recording Peripheral APRP |

| UDA1340 | Low-voltage low-power stereo audio CODEC with DSP features |

| UDA1340M | Low-voltage low-power stereo audio CODEC with DSP features |

相關代理商/技術參數 |

參數描述 |

|---|---|

| UDA1334ATS | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Low power audio DAC with PLL |

| UDA1334ATS/N2 | 制造商:NXP Semiconductors 功能描述:IC DAC AUDIO LP 16-SSOP 制造商:NXP Semiconductors 功能描述:IC, DAC, AUDIO, LP, 16-SSOP |

| UDA1334ATS/N2,112 | 功能描述:數模轉換器- DAC AUDIO DAC LP RoHS:否 制造商:Texas Instruments 轉換器數量:1 DAC 輸出端數量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| UDA1334ATS/N2,118 | 功能描述:數模轉換器- DAC ULTRA LOW COST DAC RoHS:否 制造商:Texas Instruments 轉換器數量:1 DAC 輸出端數量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

| UDA1334ATSDH | 功能描述:數模轉換器- DAC AUDIO DAC LP RoHS:否 制造商:Texas Instruments 轉換器數量:1 DAC 輸出端數量:1 轉換速率:2 MSPs 分辨率:16 bit 接口類型:QSPI, SPI, Serial (3-Wire, Microwire) 穩定時間:1 us 最大工作溫度:+ 85 C 安裝風格:SMD/SMT 封裝 / 箱體:SOIC-14 封裝:Tube |

發布緊急采購,3分鐘左右您將得到回復。