- 您現在的位置:買賣IC網 > PDF目錄383981 > UPD2845GR-E2 (NEC Corp.) 1 V, 1.3 mA, 94MHz PLL SYNTHESIZER LSI FOR PAGER SYSTEM PDF資料下載

參數資料

| 型號: | UPD2845GR-E2 |

| 廠商: | NEC Corp. |

| 英文描述: | 1 V, 1.3 mA, 94MHz PLL SYNTHESIZER LSI FOR PAGER SYSTEM |

| 中文描述: | 1伏,1.3毫安,94MHz PLL頻率合成器大規模集成電路的尋呼系統 |

| 文件頁數: | 1/16頁 |

| 文件大小: | 144K |

| 代理商: | UPD2845GR-E2 |

DATA SHEET

CMOS DIGITAL INTEGRATED CIRCUITS

P

PD2845GR

1 V, 1.3 mA, 94MHz PLL SYNTHESIZER LSI

FOR PAGER SYSTEM

1994

Document No. P12150EJ2V0DS00 (2nd edition)

(Previous No. IC-3291)

Date Published February 1997 N

P i

d i J

DESCRIPTION

P

PD2845GR is a PLL synthesizer LSI for pager system. This LSI is manufactured using low voltage CMOS

process and therefore realized the low power consumption PLL operated on 1 V, 1.3 mA. This LSI is packaged in 16

pin plastic SSOP suitable for high-density surface mounting. So, this product contributes to produce a long-life-

battery and physically-small pager system.

FEATURES

Operating frequency : · Input frequency : f

in

= 10 MHz to 94 MHz

· Reference oscillating frequency

Low Supply voltage

: · PLL block : V

DD1

= 1.00 V to 1.15 V @ f

in

= 10 MHz to 70 MHz

V

DD1

= 1.05 V to 1.15 V @ f

in

= 10 MHz to 94 MHz

· Charge pump block: V

DD2

= 3.0 V ± 300 mV

Low power consumption

I

DD

= 1.3 mA TYP. @ f

in

= 70 MHz, f

x’tal

= 12.8 MHz

Equipped with power-save function

Serial data can be received in power-save mode.

Packaged in 16 pin plastic SSOP suitable for high-density surface mounting.

: f

x’tal

= 12.8 MHz

ORDERING INFORMATION

PART NUMBER

PACKAGE

SUPPLYING FORM

P

PD2845GR-E1

16 pin plastic SSOP

(225 mil)

Embossed tape 12 mm wide. QTY 2.5 k/reel

Pin 1 is in tape pull-out direction.

P

PD2845GR-E2

16 pin plastic SSOP

(225 mil)

Embossed tape 12 mm wide. QTY 2.5 k/reel

Pin 1 is in tape roll-in direction.

* To order evaluation samples, please contact your local NEC sales office (Order number :

P

PD2845GR).

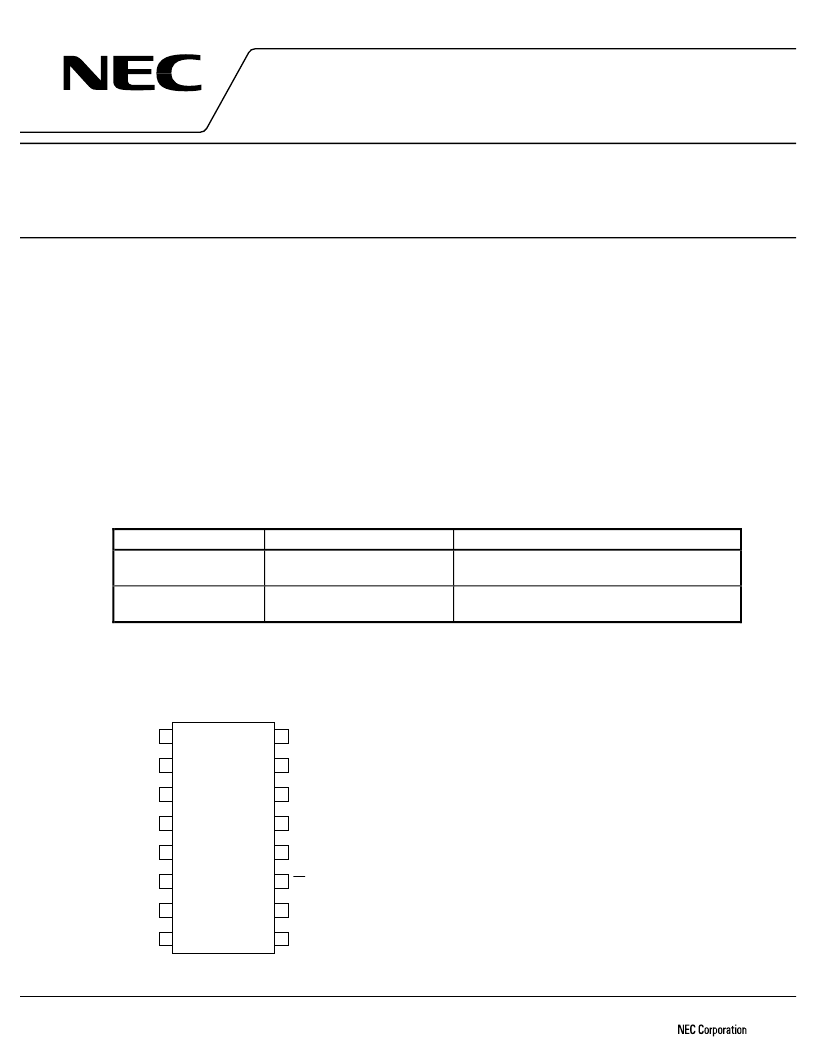

PIN ASSIGNMENT

V

DD1

F

IN

GND

FR

RESET

EO

EOP

EON

XI

XO

LE

CLK

DATA

PS

NC

V

DD2

(Top View)

Caution Electro-static sensitive devices

相關PDF資料 |

PDF描述 |

|---|---|

| UPD2845GR | 1 V, 1.3 mA, 94MHz PLL SYNTHESIZER LSI FOR PAGER SYSTEM |

| UPD3739D | 5000 PIXELS CCD LINEAR IMAGE SENSOR |

| UPD3753CY-A | 2088 PIXELS CCD LINEAR IMAGE SENSOR WITH PERIPHERAL CIRCUIT |

| UPD3753CY | 2088-BIT CCD LINEAR IMAGE SENSOR WITH PERIPHERAL CIRCUIT |

| UPD3753 | 2088-BIT CCD LINEAR IMAGE SENSOR WITH PERIPHERAL CIRCUIT |

相關代理商/技術參數 |

參數描述 |

|---|---|

| UPD28C04 | 制造商:NEC 制造商全稱:NEC 功能描述:CMOS EEPROM |

| UPD28C04C-20 | 制造商:NEC 制造商全稱:NEC 功能描述:CMOS EEPROM |

| UPD28C04C-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 EEPROM |

| UPD28C04G-20 | 制造商:NEC 制造商全稱:NEC 功能描述:CMOS EEPROM |

| UPD28C04G-25 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:x8 EEPROM |

發布緊急采購,3分鐘左右您將得到回復。