- 您現在的位置:買賣IC網 > PDF目錄140370 > WEDPZ512K72V-100BC (WHITE ELECTRONIC DESIGNS CORP) 512K X 72 ZBT SRAM, 5 ns, PBGA152 PDF資料下載

參數資料

| 型號: | WEDPZ512K72V-100BC |

| 廠商: | WHITE ELECTRONIC DESIGNS CORP |

| 元件分類: | SRAM |

| 英文描述: | 512K X 72 ZBT SRAM, 5 ns, PBGA152 |

| 封裝: | 17 X 23 MM, PLASTIC, BGA-152 |

| 文件頁數: | 1/15頁 |

| 文件大小: | 0K |

| 代理商: | WEDPZ512K72V-100BC |

1

White Electronic Designs Corporation (602) 437-1520 www.wedc.com

White Electronic Designs

WEDPZ512K72V-XBX

February 2009

Rev. 9

FEATURES

Fast clock speed: 150, 133, and 100MHz

Fast access times: 3.8ns, 4.2ns, and 5.0ns

Fast OE# access times: 3.8ns, 4.2ns, and 5.0ns

High performance 3-1-1-1 access rate

3.3V ± 5% power supply

I/O supply voltage 3.3V or 2.5V

Common data inputs and data outputs

Byte write enable and global write control

Six chip enables for depth expansion and

address pipeline

Internally self-timed write cycle

Burst control pin (interleaved or linear burst

sequence)

Automatic power-down for portable applications

Commercial, industrial and military temperature

ranges

Packaging:

152 PBGA package 17 x 23mm

BENEFITS

30% space savings compared to equivalent

TQFP solution

Reduced part count

24% I/O reduction

Laminate interposer for optimum TCE match

Low Prole

Reduce layer count for board routing

Suitable for hi-reliability applications

User congurable as 1M x 36 or 2M x 18

Upgradable to 1M x 72 (contact factory for availability)

512K x 72 Synchronous Pipeline Burst ZBL SRAM

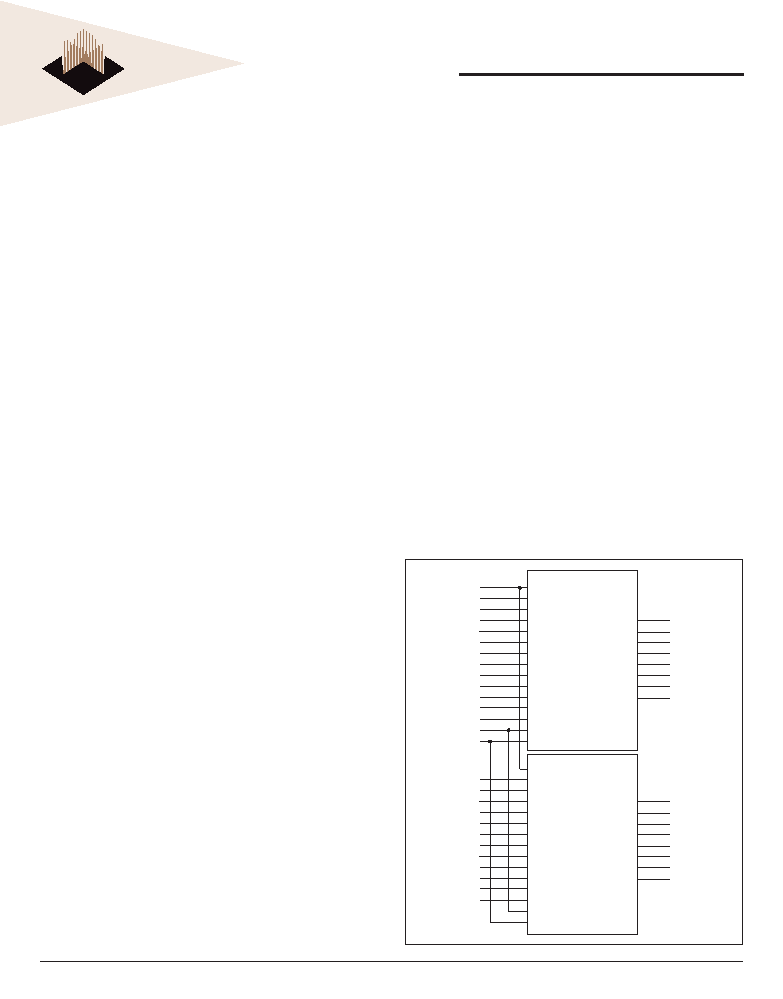

FUNCTIONAL BLOCK DIAGRAM

DESCRIPTION

The WEDC SyncBurst - SRAM employs high-speed,

low-power CMOS design that is fabricated using an

advanced CMOS process. WEDC’s 32Mb SyncBurst

SRAMs integrate two 512K x 36 SSRAMs into a single

BGA package to provide 512K x 72 conguration. All

synchronous inputs pass through registers controlled by a

positive-edge-triggered single-clock input (CLK). The ZBL

or Zero Bus Latency Memory utilizes all the bandwidth

in any combination of operating cycles. Address, data

inputs, and all control signals except output enable and

linear burst order are synchronized to input clock. Burst

order control must be tied “High or Low.” Asynchronous

inputs include the sleep mode enable (ZZ). Output Enable

controls the outputs at any given time. Write cycles are

internally self-timed and initiated by the rising edge of the

clock input. This feature eliminates complex off-chip write

pulse generation and provides increased timing exibility

for incoming signals.

* Product is subject to change without notice.

A0-18

BWa#

BWb#

BWc#

BWd#

WE0#

OE0#

CLK0

CKE0#

CS10#

CS20#

CS20

ADV0

LBO#

ZZ

SA

BWa#

BWb#

BWc#

BWd#

WE0#

OE0#

CLK

CKE#

CS1#

CS2#

CS2

ADV

LBO#

ZZ

DQPA

DQA0-7

DQPB

DQB0-7

DQPC

DQC0-7

DQPD

DQD0-7

DQPA

DQA0-7

DQPB

DQB0-7

DQPC

DQC0-7

DQPD

DQD0-7

512K x 36 SSRAM

BWe#

BWf#

BWg#

BWh#

WE1#

OE1#

CLK1#

CKE1#

CS11#

CS21#

CS21

ADV1

SA

BWa#

BWb#

BWc#

BWd#

WEO#

OEO#

CLK

CKE

CS1#

CS2#

CS2

ADV

LBO#

ZZ

512K x 36 SSRAM

DQPA

DQA0-7

DQPB

DQB0-7

DQPC

DQC0-7

DQPH

DQD0-7

DQPE

DQE0-7

DQPF

DQF0-7

DQPG

DQG0-7

DQPH

DQH0-7

相關PDF資料 |

PDF描述 |

|---|---|

| WS128K32-20G1UC | 128K X 32 MULTI DEVICE SRAM MODULE, 20 ns, CQFP68 |

| WS128K32-25G1TCA | 128K X 32 MULTI DEVICE SRAM MODULE, 25 ns, CQFP68 |

| WS128K32-25G1TQA | 128K X 32 MULTI DEVICE SRAM MODULE, 25 ns, CQFP68 |

| WS128K32-35G1UM | 128K X 32 MULTI DEVICE SRAM MODULE, 35 ns, CQFP68 |

| WS128K32-55G1TMA | 128K X 32 MULTI DEVICE SRAM MODULE, 55 ns, CQFP68 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| WEDPZ512K72V-100BI | 制造商:Microsemi Corporation 功能描述:512K X 72 ZBL SSRAM MODULE, 3.3V, 100MHZ, 152 BGA 17MM X 23M - Bulk |

| WEDPZ512K72V-100BM | 制造商:Microsemi Corporation 功能描述:512K X 72 ZBL SSRAM MODULE, 3.3V, 100MHZ, 152 BGA 17MM X 23M - Bulk |

| WEDPZ512K72V-133BC | 制造商:Microsemi Corporation 功能描述:512K X 72 ZBL SSRAM MODULE, 3.3V, 133MHZ, 152 BGA 17MM X 23M - Bulk |

| WEDPZ512K72V-133BI | 制造商:Microsemi Corporation 功能描述:512K X 72 ZBL SSRAM MODULE, 3.3V, 133MHZ, 152 BGA 17MM X 23M - Bulk |

| WEDPZ512K72V-133BM | 制造商:Microsemi Corporation 功能描述:512K X 72 ZBL SSRAM MODULE, 3.3V, 133MHZ, 152 BGA 17MM X 23M - Bulk |

發布緊急采購,3分鐘左右您將得到回復。