- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄376449 > X98021L128-3.3-Z (INTERSIL CORP) 210MHz Triple Video Digitizer with Digital PLL PDF資料下載

參數(shù)資料

| 型號(hào): | X98021L128-3.3-Z |

| 廠商: | INTERSIL CORP |

| 元件分類: | 消費(fèi)家電 |

| 英文描述: | 210MHz Triple Video Digitizer with Digital PLL |

| 中文描述: | SPECIALTY CONSUMER CIRCUIT, PQFP128 |

| 封裝: | 14 X 20 MM, ROHS COMPLIANT, MS-022, MQFP-128 |

| 文件頁(yè)數(shù): | 1/29頁(yè) |

| 文件大小: | 294K |

| 代理商: | X98021L128-3.3-Z |

當(dāng)前第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)

1

FN8219.0

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures.

1-888-INTERSIL or 1-888-468-3774 | Intersil (and design) is a registered trademark of Intersil Americas Inc.

Copyright Intersil Americas Inc. 2005. All Rights Reserved

All other trademarks mentioned are the property of their respective owners.

X98021

210MHz Triple Video Digitizer with

Digital PLL

The X98021 3-channel, 8-bit Analog Front End (AFE)

contains all the components necessary to digitize analog

RGB or YUV graphics signals from personal computers,

workstations and video set-top boxes. The fully differential

analog design provides high PSRR and dynamic

performance to meet the stringent requirements of the

graphics display industry. The AFE’s 210MSPS conversion

rate supports resolutions up to UXGA at 75Hz refresh rate,

while the front end's high input bandwidth ensures sharp

images at the highest resolutions.

To minimize noise, the X98021's analog section features 2

sets of pseudo-differential RGB inputs with programmable

input bandwidth, as well as internal DC restore clamping

(including mid-scale clamping for YUV signals). This is

followed by the programmable gain/offset stage and the

three 210MSPS Analog-to-Digital Converters (ADCs).

Automatic Black Level Compensation (ABLC

)

eliminates

part-to-part offset variation, ensuring perfect black level

performance in every application.

The X98021's digital PLL generates a pixel clock from the

analog source's HSYNC or SOG (Sync-On-Green) signals.

Pixel clock output frequencies range from 10MHz to 210MHz

with sampling clock jitter of 250ps peak to peak.

Features

210MSPS maximum conversion rate

Low PLL clock jitter (250ps p-p @ 210MSPS)

64 interpixel sampling positions

0.35V

p-p

to 1.4V

p-p

video input range

Programmable bandwidth (100MHz to 780MHz)

2 channel input multiplexer

RGB and YUV 4:2:2 output formats

5 embedded voltage regulators allow operation from

single 3.3V supply and enhance performance, isolation

Completely independent 8 bit gain/10 bit offset control

CSYNC and SOG support

Trilevel sync detection

1.1W typical P

D

@ 210MSPS

Pb-free plus anneal available (RoHS compliant)

Applications

LCD Monitors and Projectors

Digital TVs

Plasma Display Panels

RGB Graphics Processing

Scan Converters

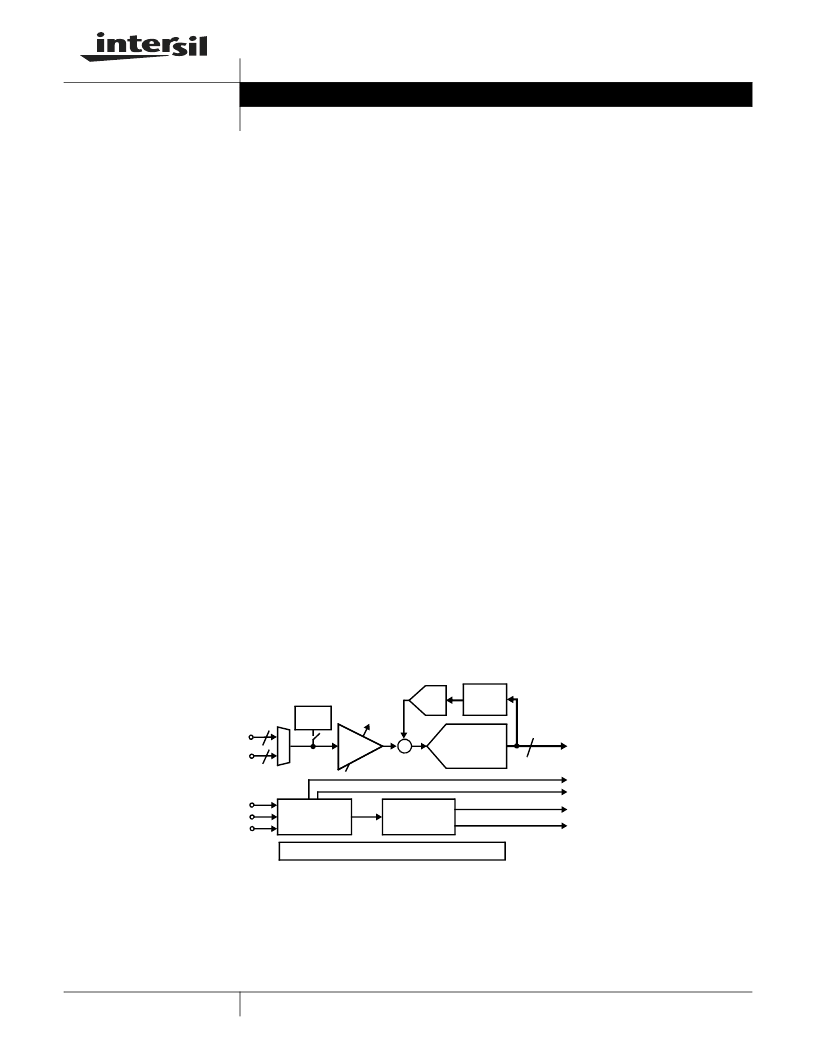

Simplified Block Diagram

RGB/YPbPr

IN

1

PGA

8 bit ADC

Offset

DAC

ABLC

8 or 16

x3

SOG

IN

1/2

HSYNC

IN

1/2

VSYNC

IN

/2

Sync

Processing

Digital PLL

Voltage

Clamp

RGB/YPbPr

IN

2

3

3

RGB/YUV

OUT

PIXELCLK

OUT

HS

OUT

HSYNC

OUT

VSYNC

OUT

AFE Configuration and Control

+

Data Sheet

June 2, 2005

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| X98024 | 240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3 | 240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3-Z | 240MHz Triple Video Digitizer with Digital PLL |

| XC145481 | 3 V PCM Codec-Filter |

| XC145481DW | 3 V PCM Codec-Filter |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| X98024 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024_06 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3 | 制造商:INTERSIL 制造商全稱:Intersil Corporation 功能描述:240MHz Triple Video Digitizer with Digital PLL |

| X98024L128-3.3-Z | 功能描述:IC TRPL VID DIGITIZER 128MQFP RoHS:是 類別:集成電路 (IC) >> 線性 - 視頻處理 系列:- 標(biāo)準(zhǔn)包裝:250 系列:- 類型:電平移位器 應(yīng)用:LCD 電視機(jī)/監(jiān)控器 安裝類型:表面貼裝 封裝/外殼:28-WFQFN 裸露焊盤 供應(yīng)商設(shè)備封裝:28-WQFN(4x4)裸露焊盤 包裝:帶卷 (TR) 其它名稱:296-32523-2TPS65198RUYT-ND |

| X98027 | 制造商:XICOR 制造商全稱:Xicor Inc. 功能描述:PRELIMINARY INFORMATION |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。