- 您現在的位置:買賣IC網 > PDF目錄21989 > XC2S50-5PQG208C (Xilinx Inc)IC SPARTAN-II FPGA 50K 208-PQFP PDF資料下載

參數資料

| 型號: | XC2S50-5PQG208C |

| 廠商: | Xilinx Inc |

| 文件頁數: | 41/99頁 |

| 文件大小: | 0K |

| 描述: | IC SPARTAN-II FPGA 50K 208-PQFP |

| 標準包裝: | 24 |

| 系列: | Spartan®-II |

| LAB/CLB數: | 384 |

| 邏輯元件/單元數: | 1728 |

| RAM 位總計: | 32768 |

| 輸入/輸出數: | 140 |

| 門數: | 50000 |

| 電源電壓: | 2.375 V ~ 2.625 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 208-BFQFP |

| 供應商設備封裝: | 208-PQFP(28x28) |

| 產品目錄頁面: | 599 (CN2011-ZH PDF) |

| 其它名稱: | 122-1320 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁當前第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁

Spartan-II FPGA Family: Functional Description

DS001-2 (v2.8) June 13, 2008

Module 2 of 4

Product Specification

46

R

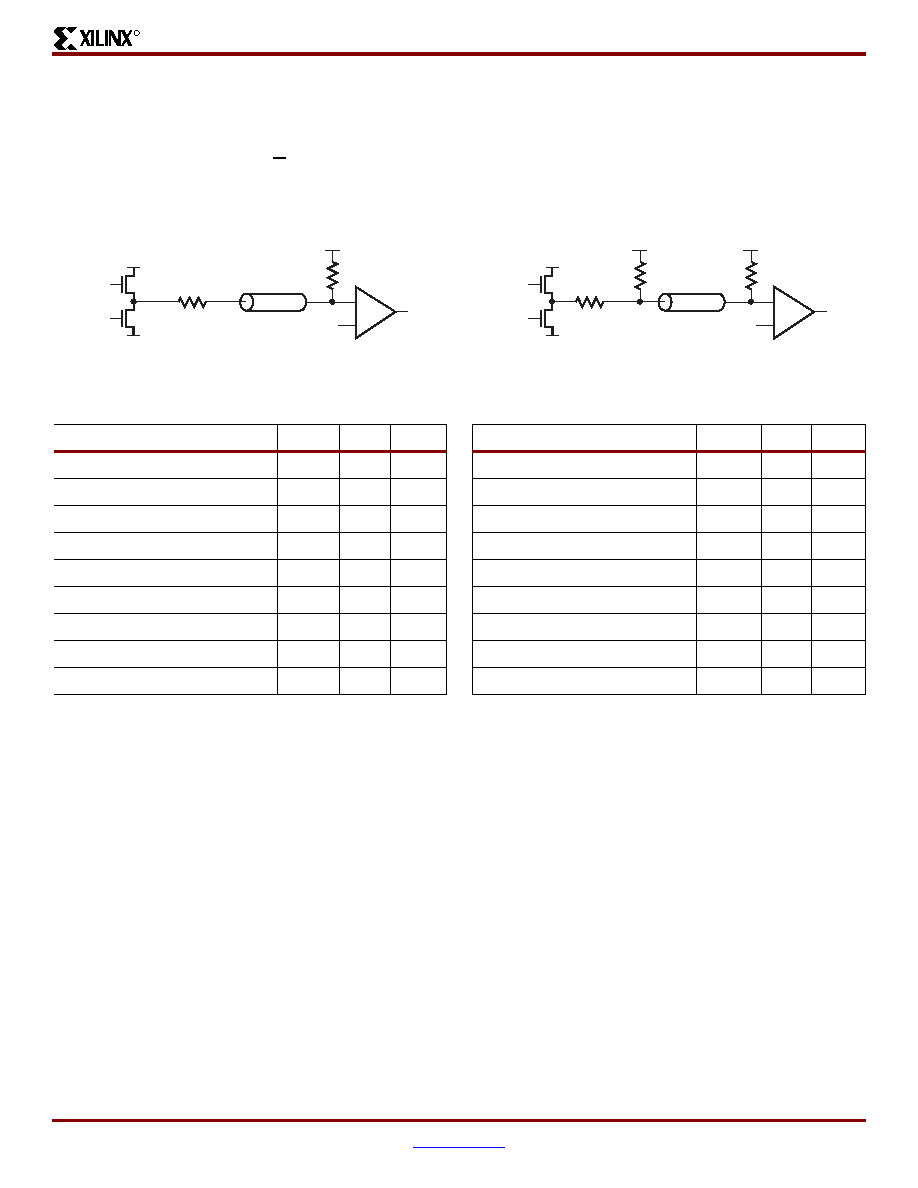

SSTL3 Class I

A sample circuit illustrating a valid termination technique for

SSTL3_I appears in Figure 47. DC voltage specifications

Specifications" in Module 3 for the actual FPGA

characteristics.

SSTL3 Class II

A sample circuit illustrating a valid termination technique for

SSTL3_II appears in Figure 48. DC voltage specifications

Specifications" in Module 3 for the actual FPGA

characteristics.

Figure 47: Terminated SSTL3 Class I

Table 25: SSTL3_I Voltage Specifications

Parameter

Min

Typ

Max

VCCO

3.0

3.3

3.6

VREF = 0.45 × VCCO

1.3

1.5

1.7

VTT = VREF

1.3

1.5

1.7

VIH ≥ VREF + 0.2

1.5

1.7

3.9(1)

VIL ≤ VREF – 0.2

–0.3(2)

1.3

1.5

VOH ≥ VREF + 0.6

1.9

-

VOL ≤ VREF – 0.6

-

1.1

IOH at VOH (mA)

–8

-

IOL at VOL (mA)

8

-

Notes:

1.

VIH maximum is VCCO + 0.3.

2.

VIL minimum does not conform to the formula.

VREF = 1.5V

VCCO = 3.3V

50

Ω

Z = 50

SSTL3 Class I

DS001_47_061200

VTT = 1.5V

25

Ω

Figure 48: Terminated SSTL3 Class II

Table 26: SSTL3_II Voltage Specifications

Parameter

Min

Typ

Max

VCCO

3.0

3.3

3.6

VREF = 0.45 × VCCO

1.3

1.5

1.7

VTT = VREF

1.3

1.5

1.7

VIH ≥ VREF + 0.2

1.5

1.7

3.9(1)

VIL ≤ VREF – 0.2

–0.3(2)

1.3

1.5

VOH ≥ VREF + 0.8

2.1

-

VOL ≤ VREF – 0.8

-

0.9

IOH at VOH (mA)

–16

-

IOL at VOL (mA)

16

-

Notes:

1.

VIH maximum is VCCO + 0.3

2.

VIL minimum does not conform to the formula

VREF = 1.5V

VCCO = 3.3V

50

Ω

Z = 50

SSTL3 Class II

DS001_48_061200

VTT = 1.5V

50

Ω

VTT = 1.5V

25

Ω

相關PDF資料 |

PDF描述 |

|---|---|

| FMC13DRYN-S734 | CONN EDGECARD 26POS DIP .100 SLD |

| TACR336M010RTA | CAP TANT 33UF 10V 20% 0805 |

| XC3S250E-4VQG100C | IC SPARTAN-3E FPGA 250K 100VQFP |

| FMC13DRYH-S734 | CONN EDGECARD 26POS DIP .100 SLD |

| XC3S100E-4TQG144I | IC FPGA SPARTAN-3E 100K 144-TQFP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| XC2S50-5PQG208I | 制造商:Xilinx 功能描述:FPGA SPARTAN-II 50K GATES 1728 CELLS 263MHZ 2.5V 208PQFP - Trays |

| XC2S50-5TQ144C | 功能描述:IC FPGA 2.5V 384 CLB'S 144-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:Spartan®-II 標準包裝:40 系列:Spartan® 6 LX LAB/CLB數:3411 邏輯元件/單元數:43661 RAM 位總計:2138112 輸入/輸出數:358 門數:- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應商設備封裝:676-FBGA(27x27) |

| XC2S50-5TQ144C-ES | 制造商:Xilinx 功能描述:2S50-5TQ144C-ES |

| XC2S50-5TQ144I | 功能描述:IC FPGA 2.5V I-TEMP 144-TQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:Spartan®-II 標準包裝:40 系列:Spartan® 6 LX LAB/CLB數:3411 邏輯元件/單元數:43661 RAM 位總計:2138112 輸入/輸出數:358 門數:- 電源電壓:1.14 V ~ 1.26 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:676-BGA 供應商設備封裝:676-FBGA(27x27) |

| XC2S50-5TQG144C | 功能描述:IC SPARTAN-II FPGA 50K 144-TQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:Spartan®-II 標準包裝:60 系列:XP LAB/CLB數:- 邏輯元件/單元數:10000 RAM 位總計:221184 輸入/輸出數:244 門數:- 電源電壓:1.71 V ~ 3.465 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:388-BBGA 供應商設備封裝:388-FPBGA(23x23) 其它名稱:220-1241 |

發布緊急采購,3分鐘左右您將得到回復。