- 您現在的位置:買賣IC網 > PDF目錄374970 > XC2S50ESERIES (Xilinx, Inc.) Spartan-IIE 1.8V FPGA Family: Introduction and Ordering Information PDF資料下載

參數資料

| 型號: | XC2S50ESERIES |

| 廠商: | Xilinx, Inc. |

| 英文描述: | Spartan-IIE 1.8V FPGA Family: Introduction and Ordering Information |

| 中文描述: | 的Spartan - IIE 1.8V的FPGA系列:介紹和訂購信息 |

| 文件頁數: | 1/4頁 |

| 文件大小: | 114K |

| 代理商: | XC2S50ESERIES |

DS077-1 (v1.0) November 15, 2001

Preliminary Product Specification

1-800-255-77781

2001 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at

http://www.xilinx.com/legal.htm

.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

Introduction

The Spartan-IIE 1.8V Field-Programmable Gate Array

family gives users high performance, abundant logic

resources, and a rich feature set, all at an exceptionally low

price. The five-member family offers densities ranging from

50,000 to 300,000 system gates, as shown in

Table 1

. Sys-

tem performance is supported beyond 200 MHz.

Spartan-IIE devices deliver more gates, I/Os, and features

per dollar than other FPGAs by combining advanced pro-

cess technology with a streamlined architecture based on

the proven Virtex-E platform. Features include block RAM

(to 64K bits), distributed RAM (to 98,304 bits), 19 selectable

I/O standards, and four DLLs (Delay-Locked Loops). Fast,

predictable interconnect means that successive design iter-

ations continue to meet timing requirements.

The Spartan-IIE family is a superior alternative to

mask-programmed ASICs. The FPGA avoids the initial cost,

lengthy development cycles, and inherent risk of

conventional ASICs. Also, FPGA programmability permits

design upgrades in the field with no hardware replacement

necessary (impossible with ASICs).

Features

Second generation ASIC replacement technology

-

Densities as high as 6,912 logic cells with up to

300,000 system gates

-

Streamlined features based on Virtex-E

architecture

-

Unlimited in-system reprogrammability

-

Very low cost

System level features

-

SelectRAM+ hierarchical memory:

·

16 bits/LUT distributed RAM

·

Configurable 4K-bit true dual-port block RAM

·

Fast interfaces to external RAM

-

Fully 3.3V PCI compliant to 64 bits at 66 MHz and

CardBus compliant

-

Low-power segmented routing architecture

-

Full readback ability for verification/observability

-

Dedicated carry logic for high-speed arithmetic

-

Efficient multiplier support

-

Cascade chain for wide-input functions

-

Abundant registers/latches with enable, set, reset

-

Four dedicated DLLs for advanced clock control

-

Four primary

low-skew

global

clock

distribution

nets

-

IEEE 1149.1 compatible boundary scan logic

Versatile I/O and packaging

-

Low cost packages available in all densities

-

Family footprint compatibility in common packages

-

19 high-performance interface standards, including

LVDS and LVPECL

-

Up to 120 differential I/O pairs that can be input,

output, or bidirectional

-

Zero hold time simplifies system timing

Fully supported by powerful Xilinx ISE development

system

-

Fully automatic mapping, placement, and routing

-

Integrated with design entry and verification tools

0

Spartan-IIE 1.8V FPGA Family:

Introduction and Ordering

Information

Preliminary Product Specification

DS077-1 (v1.0) November 15, 2001

0

0

R

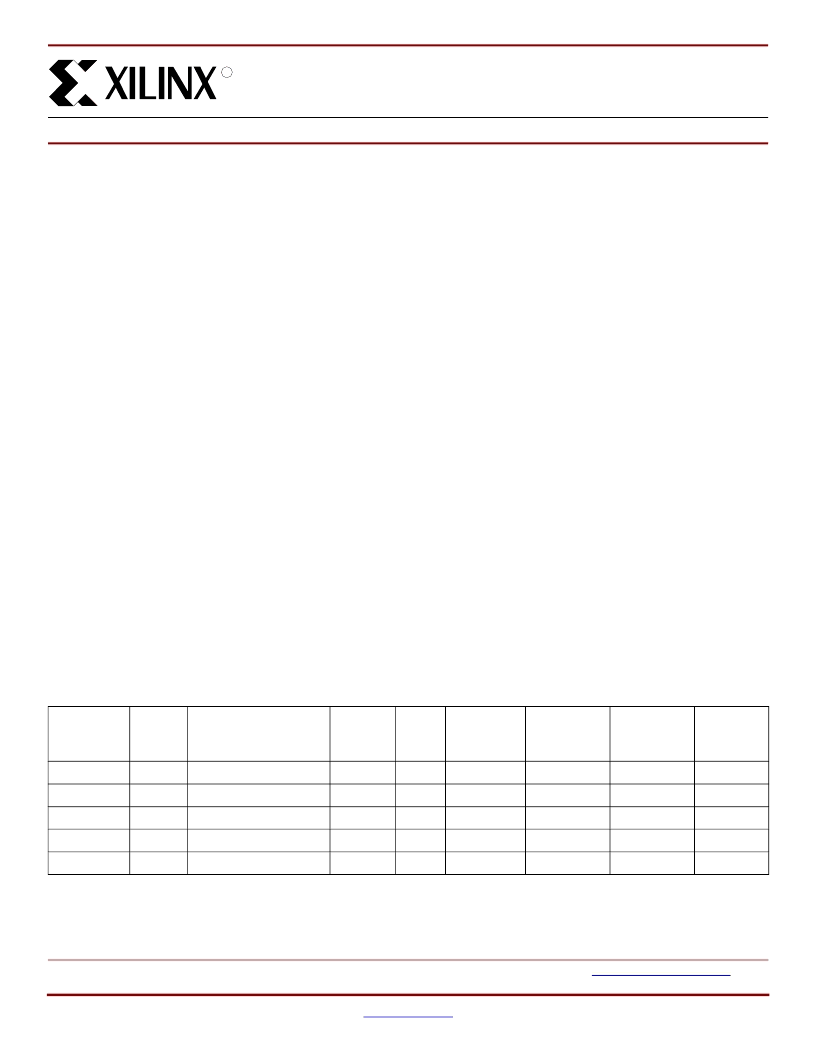

Table 1:

Spartan-IIE FPGA Family Members

Device

Logic

Cells

Typical

System Gate Range

(Logic and RAM)

CLB

Array

(R x C)

Total

CLBs

Maximum

Available

User I/O

Maximum

Differential

I/O Pairs

Distributed

RAM Bits

Block

RAM Bits

XC2S50E

1,728

23,000 - 50,000

16 x 24

384

182

84

24,576

32K

XC2S100E

2,700

37,000 - 100,000

20 x 30

600

202

86

38,400

40K

XC2S150E

3,888

52,000 - 150,000

24 x 36

864

263

114

55,296

48K

XC2S200E

5,292

71,000 - 200,000

28 x 42

1,176

289

120

75,264

56K

XC2S300E

6,912

93,000 - 300,000

32 x 48

1,536

329

120

98,304

64K

相關PDF資料 |

PDF描述 |

|---|---|

| XC2S150E-7PQ208C | Spartan-IIE 1.8V FPGA Family |

| XC2S100E-6TQ144C | CLAMP |

| XC2S100E-6TQ144I | CLAMP |

| XC2S100E-7FG456C | CLAMP |

| XC2S100E-7FG456I | CLAMP |

相關代理商/技術參數 |

參數描述 |

|---|---|

| XC2S600E | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S600E-6FG456C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Spartan-IIE FPGA |

| XC2S600E-6FG456I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

| XC2S600E-6FG456Q | 功能描述:IC FPGA SPARTAN-IIE 456FPBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現場可編程門陣列) 系列:Spartan®-IIE 產品變化通告:Step Intro and Pkg Change 11/March/2008 標準包裝:1 系列:Virtex®-5 SXT LAB/CLB數:4080 邏輯元件/單元數:52224 RAM 位總計:4866048 輸入/輸出數:480 門數:- 電源電壓:0.95 V ~ 1.05 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:1136-BBGA,FCBGA 供應商設備封裝:1136-FCBGA 配用:568-5088-ND - BOARD DEMO DAC1408D750122-1796-ND - EVALUATION PLATFORM VIRTEX-5 |

| XC2S600E-6FG676C | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:FPGA |

發布緊急采購,3分鐘左右您將得到回復。