- 您現(xiàn)在的位置:買賣IC網 > PDF目錄371340 > XC5215-3PG299I Field Programmable Gate Array (FPGA) PDF資料下載

參數(shù)資料

| 型號: | XC5215-3PG299I |

| 英文描述: | Field Programmable Gate Array (FPGA) |

| 中文描述: | 現(xiàn)場可編程門陣列(FPGA) |

| 文件頁數(shù): | 1/73頁 |

| 文件大小: | 598K |

| 代理商: | XC5215-3PG299I |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁

November 5, 1998 (Version 5.2)

7-83

7

Features

Low-cost, register/latch rich, SRAM based

reprogrammable architecture

-

0.5

μ

m three-layer metal CMOS process technology

-

256 to 1936 logic cells (3,000 to 23,000 “gates”)

-

Price competitive with Gate Arrays

System Level Features

-

System performance beyond 50 MHz

-

6 levels of interconnect hierarchy

-

VersaRing

I/O Interface for pin-locking

-

Dedicated carry logic for high-speed arithmetic

functions

-

Cascade chain for wide input functions

-

Built-in IEEE 1149.1 JTAG boundary scan test

circuitry on all I/O pins

-

Internal 3-state bussing capability

-

Four dedicated low-skew clock or signal distribution

nets

Versatile I/O and Packaging

-

Innovative VersaRing

I/O interface provides a high

logic cell to I/O ratio, with up to 244 I/O signals

-

Programmable output slew-rate control maximizes

performance and reduces noise

-

Zero Flip-Flop hold time for input registers simplifies

system timing

-

Independent Output Enables for external bussing

-

Footprint compatibility in common packages within

the XC5200 Series and with the XC4000 Series

Over 150 device/package combinations, including

advanced BGA, TQ, and VQ packaging available

Fully Supported by Xilinx Development System

-

Automatic place and route software

-

Wide selection of PC and Workstation platforms

-

Over 100 3rd-party Alliance interfaces

-

Supported by shrink-wrap Foundation software

-

Description

The XC5200 Field-Programmable Gate Array Family is

engineered to deliver low cost. Building on experiences

gained with three previous successful SRAM FPGA fami-

lies, the XC5200 family brings a robust feature set to pro-

grammable logic design. The VersaBlock

logic module,

the VersaRing I/O interface, and a rich hierarchy of inter-

connect resources combine to enhance design flexibility

and reduce time-to-market. Complete support for the

XC5200 family is delivered through the familiar Xilinx soft-

ware environment. The XC5200 family is fully supported on

popular workstation and PC platforms. Popular design

entry methods are fully supported, including ABEL, sche-

matic capture, VHDL, and Verilog HDL synthesis. Design-

ers utilizing logic synthesis can use their existing tools to

design with the XC5200 devices.

.

0

XC5200 Series

Field Programmable Gate Arrays

November 5, 1998 (Version 5.2)

0

7*

Product Specification

R

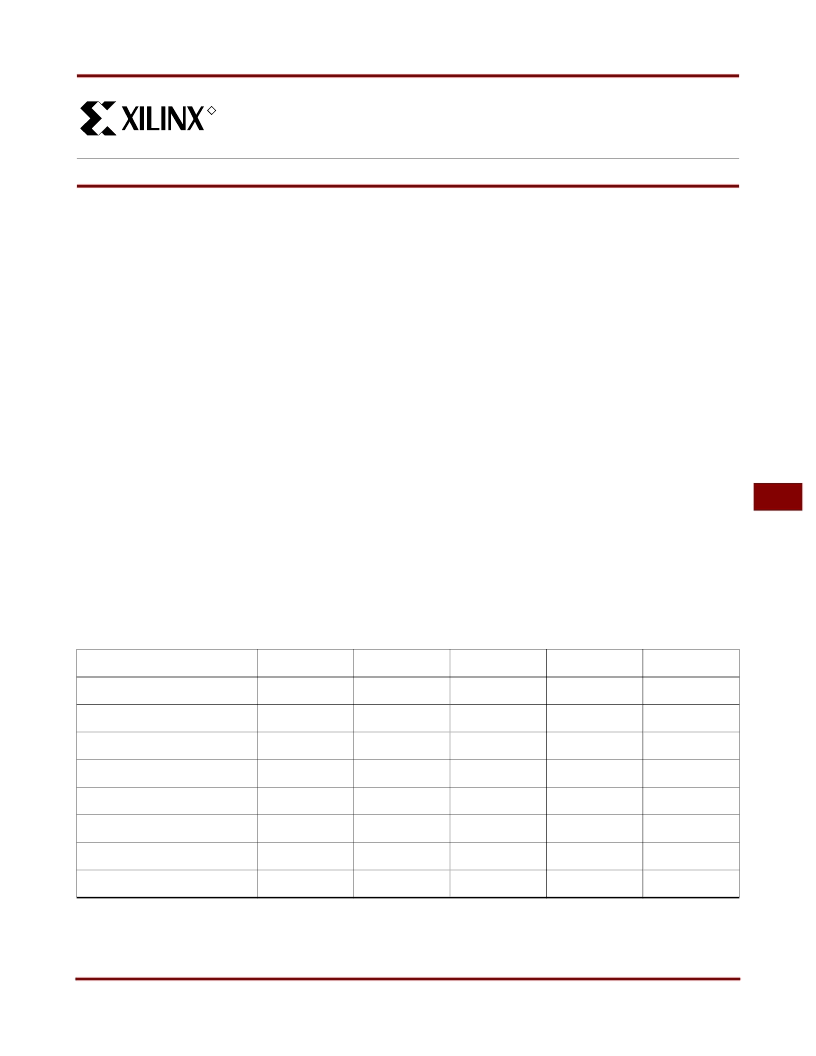

Table 1: XC5200 Field-Programmable Gate Array Family Members

Device

XC5202

XC5204

XC5206

XC5210

XC5215

Logic Cells

256

480

784

1,296

1,936

Max Logic Gates

3,000

6,000

10,000

16,000

23,000

Typical Gate Range

2,000 - 3,000

4,000 - 6,000

6,000 - 10,000

10,000 - 16,000 15,000 - 23,000

VersaBlock Array

8 x 8

10 x 12

14 x 14

18 x 18

22 x 22

CLBs

64

120

196

324

484

Flip-Flops

256

480

784

1,296

1,936

I/Os

84

124

148

196

244

TBUFs per Longline

10

14

16

20

24

相關PDF資料 |

PDF描述 |

|---|---|

| XC5215-3PQ160I | Field Programmable Gate Array (FPGA) |

| XC5215-4BG225I | Field Programmable Gate Array (FPGA) |

| XC5215-4BG352I | Field Programmable Gate Array (FPGA) |

| XC5215-5BG225I | Field Programmable Gate Array (FPGA) |

| XC5215-5BG352I | Field Programmable Gate Array (FPGA) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XC5215-3PQ100C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5215-3PQ160C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5215-3PQ160I | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| XC5215-3PQ208C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

| XC5215-3PQ240C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復。