- 您現在的位置:買賣IC網 > PDF目錄19551 > XC9536-5CS48C (Xilinx Inc)IC CPLD 36 MCELL C-TEMP 48-CSP PDF資料下載

參數資料

| 型號: | XC9536-5CS48C |

| 廠商: | Xilinx Inc |

| 文件頁數: | 1/8頁 |

| 文件大小: | 0K |

| 描述: | IC CPLD 36 MCELL C-TEMP 48-CSP |

| 產品變化通告: | Product Discontinuation 26/Oct/2011 |

| 標準包裝: | 416 |

| 系列: | XC9500 |

| 可編程類型: | 系統內可編程(最少 10,000 次編程/擦除循環) |

| 最大延遲時間 tpd(1): | 5.0ns |

| 電壓電源 - 內部: | 4.75 V ~ 5.25 V |

| 邏輯元件/邏輯塊數目: | 2 |

| 宏單元數: | 36 |

| 門數: | 800 |

| 輸入/輸出數: | 34 |

| 工作溫度: | 0°C ~ 70°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 48-FBGA,CSPBGA |

| 供應商設備封裝: | 48-CSBGA(7x7) |

| 包裝: | 托盤 |

DS064 (v7.0) May 17, 2013

1

Product Specification

1998, 2003-2006, 2013 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

– PRODUCT OBSOLETE / UNDER OBSOLESCENCE –

Features

5 ns pin-to-pin logic delays on all pins

fCNT to 100 MHz

36 macrocells with 800 usable gates

Up to 34 user I/O pins

5V in-system programmable

-

Endurance of 10,000 program/erase cycles

-

Program/erase over full commercial voltage and

temperature range

Enhanced pin-locking architecture

Flexible 36V18 Function Block

-

90 product terms drive any or all of 18 macrocells

within Function Block

-

Global and product term clocks, output enables,

set and reset signals

Extensive IEEE Std 1149.1 boundary-scan (JTAG)

support

Programmable power reduction mode in each

macrocell

Slew rate control on individual outputs

User programmable ground pin capability

Extended pattern security features for design

protection

High-drive 24 mA outputs

3.3V or 5V I/O capability

Advanced CMOS 5V FastFLASH technology

Supports parallel programming of more than one

XC9500 concurrently

Available in 44-pin PLCC, 44-pin VQFP, 48-pin CSP

packages

Description

The XC9536 is a high-performance CPLD providing

advanced in-system programming and test capabilities for

general purpose logic integration. It is comprised of eight

36V18 Function Blocks, providing 800 usable gates with

propagation delays of 5 ns. See Figure 2 for the architecture

overview.

Power Management

Power dissipation can be reduced in the XC9536 by config-

uring macrocells to standard or low-power modes of opera-

tion. Unused macrocells are turned off to minimize power

dissipation.

Operating current for each design can be approximated for

specific operating conditions using the following equation:

ICC (mA) = MCHP (1.7) + MCLP (0.9) + MC (0.006 mA/MHz) f

Where:

MCHP = Macrocells in high-performance mode

MCLP = Macrocells in low-power mode

MC = Total number of macrocells used

f = Clock frequency (MHz)

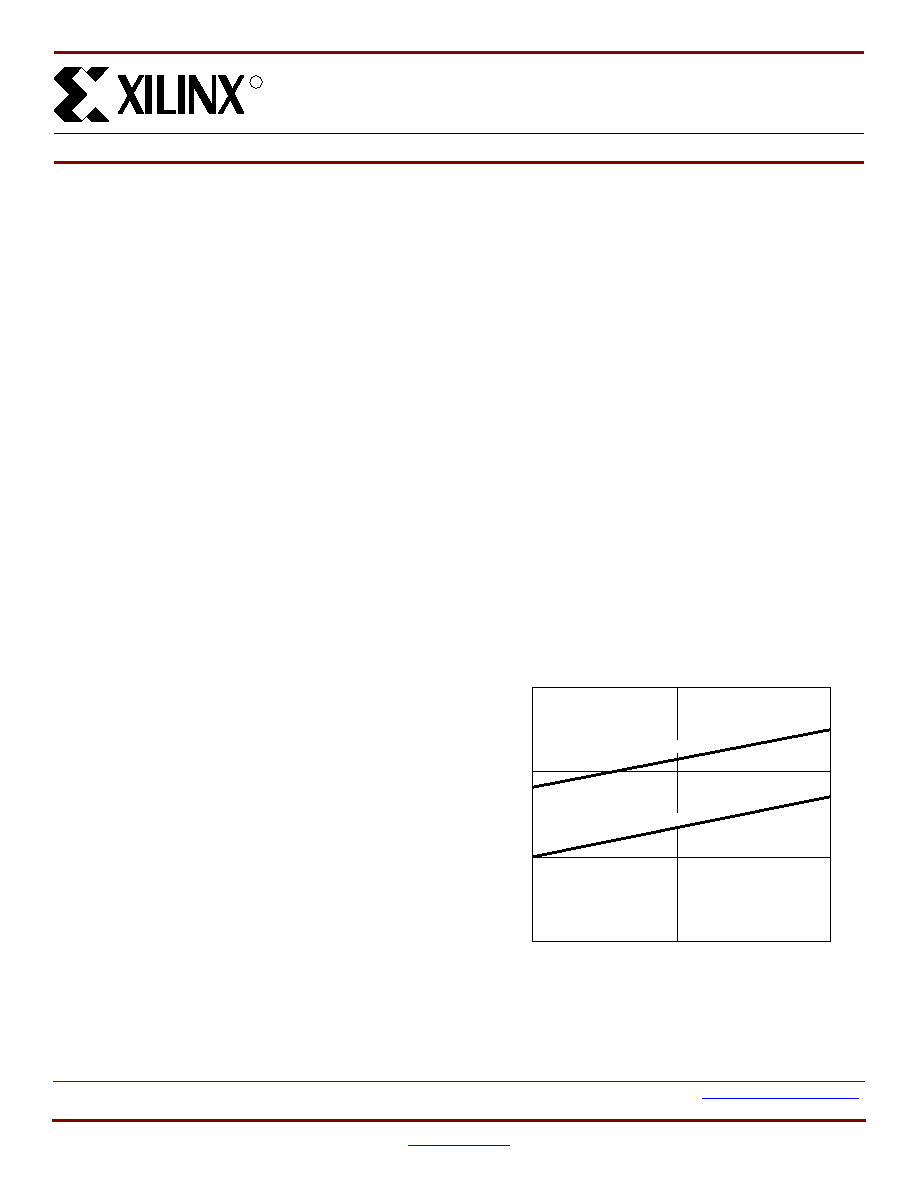

Figure 1 shows a typical calculation for the XC9536 device.

0

XC9536 In-System

Programmable CPLD

DS064 (v7.0) May 17, 2013

05

Product Specification

R

Figure 1: Typical ICC vs. Frequency for XC9536

Clock Frequency (MHz)

Typical

I

CC

(mA)

050

(50)

(30)

(83)

(50)

100

High Performance

Low Power

DS064_01_110101

相關PDF資料 |

PDF描述 |

|---|---|

| ACM22DTBN-S664 | CONN EDGECARD 44POS R/A .156 |

| RW2-1215D | CONV DC/DC 2W 9-18VIN +/-15VOUT |

| A272K15X7RK5TAA | CAP CER 2700PF 200V X7R AXIAL |

| A181M15X7RL5TAA | CAP CER 180PF 500V 20% X7R AXIAL |

| TAP686M006SRW | CAP TANT 68UF 6.3V 20% RADIAL |

相關代理商/技術參數 |

參數描述 |

|---|---|

| XC9536-5CS48I | 制造商:XILINX 制造商全稱:XILINX 功能描述:XC9536 In-System Programmable CPLD |

| XC9536-5CSG48C | 制造商:Xilinx from Components Direct 功能描述:CPLD XC9500 FAMILY 800 GATES 36 MACRO CELLS 100MHZ 0.5UM - Trays 制造商:Xilinx 功能描述:CPLD XC9500 Family 800 Gates 36 Macro Cells 100MHz 0.5um (CMOS) Technology 5V 48-Pin CSBGA |

| XC95365PC44C | 制造商:XILINX 功能描述:* |

| XC9536-5PC44C | 功能描述:IC CPLD 36 MCELL C-TEMP 44-PLCC RoHS:否 類別:集成電路 (IC) >> 嵌入式 - CPLD(復雜可編程邏輯器件) 系列:XC9500 標準包裝:24 系列:CoolRunner II 可編程類型:系統內可編程 最大延遲時間 tpd(1):7.1ns 電壓電源 - 內部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數目:24 宏單元數:384 門數:9000 輸入/輸出數:173 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:208-BFQFP 供應商設備封裝:208-PQFP(28x28) 包裝:托盤 |

| XC9536-5PC44C0090 | 制造商:Xilinx 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。