- 您現在的位置:買賣IC網 > PDF目錄19485 > XCR3064XL-7VQ100I (Xilinx Inc)IC CPLD 64 MACROCELL HP 100-VQFP PDF資料下載

參數資料

| 型號: | XCR3064XL-7VQ100I |

| 廠商: | Xilinx Inc |

| 文件頁數: | 1/12頁 |

| 文件大小: | 0K |

| 描述: | IC CPLD 64 MACROCELL HP 100-VQFP |

| 標準包裝: | 90 |

| 系列: | CoolRunner XPLA3 |

| 可編程類型: | 系統內可編程(最少 1K 次編程/擦除循環) |

| 最大延遲時間 tpd(1): | 7.0ns |

| 電壓電源 - 內部: | 2.7 V ~ 3.6 V |

| 邏輯元件/邏輯塊數目: | 4 |

| 宏單元數: | 64 |

| 門數: | 1500 |

| 輸入/輸出數: | 68 |

| 工作溫度: | -40°C ~ 85°C |

| 安裝類型: | 表面貼裝 |

| 封裝/外殼: | 100-TQFP |

| 供應商設備封裝: | 100-VQFP(14x14) |

| 包裝: | 托盤 |

DS012 (v2.5) May 26, 2009

1

Product Specification

2000–2009 Xilinx, Inc. XILINX, the Xilinx logo, Virtex, Spartan, ISE, and other designated brands included herein are trademarks of Xilinx in the United States and other

countries. All other trademarks are the property of their respective owners.

Features

Fast Zero Power (FZP) design technique provides

ultra-low power and very high speed

-

Typical Standby Current of 17 to 18

μA at 25°C

Innovative CoolRunner XPLA3 architecture

combines high speed with extreme flexibility

Based on industry's first TotalCMOS PLD — both

CMOS design and process technologies

Advanced 0.35

μ five layer metal EEPROM process

-

1,000 erase/program cycles guaranteed

-

20 years data retention guaranteed

3V, In-System Programmable (ISP) using JTAG IEEE

1149.1 interface

-

Full Boundary-Scan Test (IEEE 1149.1)

-

Fast programming times

Support for complex asynchronous clocking

-

16 product term clocks and four local control term

clocks per function block

-

Four global clocks and one universal control term

clock per device

Excellent pin retention during design changes

Available in commercial grade and extended voltage

(2.7V to 3.6V) industrial grade

5V tolerant I/O pins

Input register setup time of 2.5 ns

Single pass logic expandable to 48 product terms

High-speed pin-to-pin delays of 5.0 ns

Slew rate control per output

100% routable

Security bit prevents unauthorized access

Supports hot-plugging capability

Design entry/verification using Xilinx or industry

standard CAE tools

Innovative Control Term structure provides:

-

Asynchronous macrocell clocking

-

Asynchronous macrocell register preset/reset

-

Clock enable control per macrocell

Four output enable controls per function block

Foldback NAND for synthesis optimization

Universal 3-state which facilitates "bed of nails" testing

Available in Chip-scale BGA, Fineline BGA, and QFP

packages. Pb-free available for most package types.

See Xilinx Packaging for more information.

0

CoolRunner XPLA3 CPLD

DS012 (v2.5) May 26, 2009

014

Product Specification

R

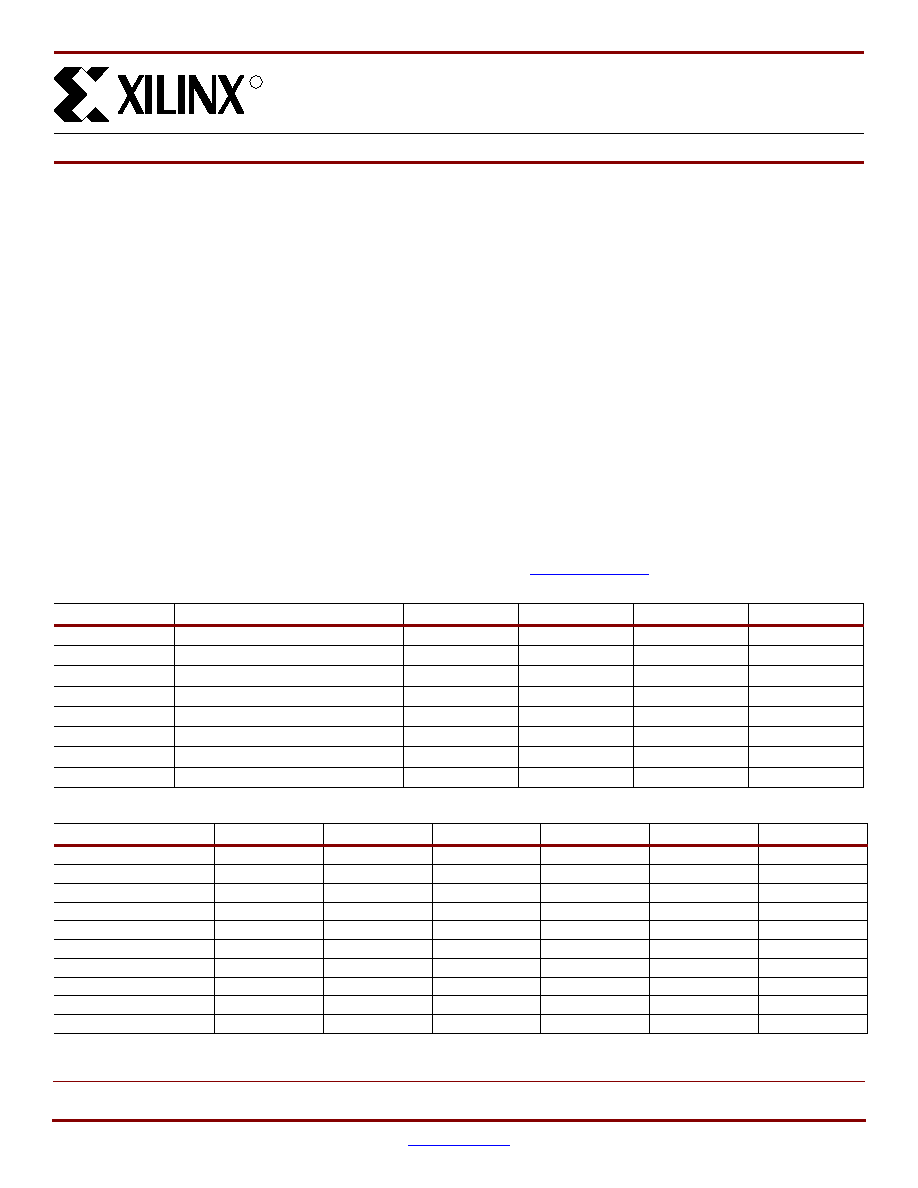

Table 1: CoolRunner XPLA3 Device Family

XCR3032XL

XCR3064XL

XCR3128XL

XCR3256XL

XCR3384XL

XCR3512XL

Macrocells

32

64

128

256

384

512

Usable Gates

750

1,500

3,000

6,000

9,000

12,000

Registers

32

64

128

256

384

512

TPD (ns)

4.55.5

5.57.0

7.0

TSU (ns)

3.0

3.5

4.3

3.8

TCO (ns)

3.5

4

4.5

5.0

Fsystem (MHz)

213

192

175

154

135

ICCSB (μA)

17

18

Table 2: CoolRunner XPLA3 Packages and User I/O Pins

XCR3032XL

XCR3064XL

XCR3128XL

XCR3256XL

XCR3384XL

XCR3512XL

44-pin VQFP

36

-

48-pin 0.8mm CSP

36

40

-

56-pin 0.5mm CSP

-

48

-

100-pin VQFP

-

68

84

-

144-pin 0.8mm CSP

-

108

-

144-pin TQFP

-

108

120

118(1)

-

208-pin PQFP

-

164

172

180

256-pin Fineline BGA

-

164

212

280-pin 0.8mm CSP

-

164

-

324-pin Fineline BGA

-

220

260

1.

XCR3384XL TQ144 JTAG pins are not compatible with other members of the CoolRunner XPLA3 family in the TQ144 package.

2.

Most packages are available in Pb-Free option. See individual data sheets for more details.

3.

The 44-pin PLCC package is discontinued per XCN07022.

相關PDF資料 |

PDF描述 |

|---|---|

| TPSC155M050R1500 | CAP TANT 1.5UF 50V 20% 2312 |

| MAX6646MUA+T | IC SENSOR REMOTE SMBUS 8UMAX |

| ADSP-BF522BBCZ-4A | IC DSP CTRLR 400MHZ 208CSPBGA |

| TPSC155K050R1500 | CAP TANT 1.5UF 50V 10% 2312 |

| ADSP-BF536BBCZ-3A | IC DSP CTLR 16BIT 182CSPBGA |

相關代理商/技術參數 |

參數描述 |

|---|---|

| XCR3064XL-7VQ44C | 功能描述:IC CPLD 64 MACROCELL HP 44-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - CPLD(復雜可編程邏輯器件) 系列:CoolRunner XPLA3 標準包裝:24 系列:CoolRunner II 可編程類型:系統內可編程 最大延遲時間 tpd(1):7.1ns 電壓電源 - 內部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數目:24 宏單元數:384 門數:9000 輸入/輸出數:173 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:208-BFQFP 供應商設備封裝:208-PQFP(28x28) 包裝:托盤 |

| XCR3064XL-7VQ44I | 功能描述:IC CPLD 64 MACROCELL HP 44-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - CPLD(復雜可編程邏輯器件) 系列:CoolRunner XPLA3 標準包裝:24 系列:CoolRunner II 可編程類型:系統內可編程 最大延遲時間 tpd(1):7.1ns 電壓電源 - 內部:1.7 V ~ 1.9 V 邏輯元件/邏輯塊數目:24 宏單元數:384 門數:9000 輸入/輸出數:173 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:208-BFQFP 供應商設備封裝:208-PQFP(28x28) 包裝:托盤 |

| XCR3064XL-7VQG100C | 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 1.5K GATES 64 MCRCLLS 166.67MHZ 0.35UM - Trays |

| XCR3064XL-7VQG100I | 制造商:Xilinx 功能描述:XLXXCR3064XL-7VQG100I IC SYSTEM GATE 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 1.5K GATES 64 MCRCLLS 166.67MHZ 0.35UM - Trays |

| XCR3064XL-7VQG44C | 制造商:Xilinx 功能描述:XLXXCR3064XL-7VQG44C IC SYSTEM GATE 制造商:Xilinx 功能描述:CPLD COOLRUNNER XPLA3 1.5K GATES 64 MCRCLLS 166.67MHZ 0.35UM - Trays |

發布緊急采購,3分鐘左右您將得到回復。