- 您現在的位置:買賣IC網 > PDF目錄248600 > 552AD000110BGR (SILICON LABORATORIES) VCXO, CLOCK, 125 MHz, LVPECL OUTPUT PDF資料下載

參數資料

| 型號: | 552AD000110BGR |

| 廠商: | SILICON LABORATORIES |

| 元件分類: | XO, clock |

| 英文描述: | VCXO, CLOCK, 125 MHz, LVPECL OUTPUT |

| 封裝: | ROHS COMPLIANT, SMD, 6 PIN |

| 文件頁數: | 1/80頁 |

| 文件大小: | 3734K |

| 代理商: | 552AD000110BGR |

當前第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁

Rev. 0.5 7/06

Copyright 2006 by Silicon Laboratories

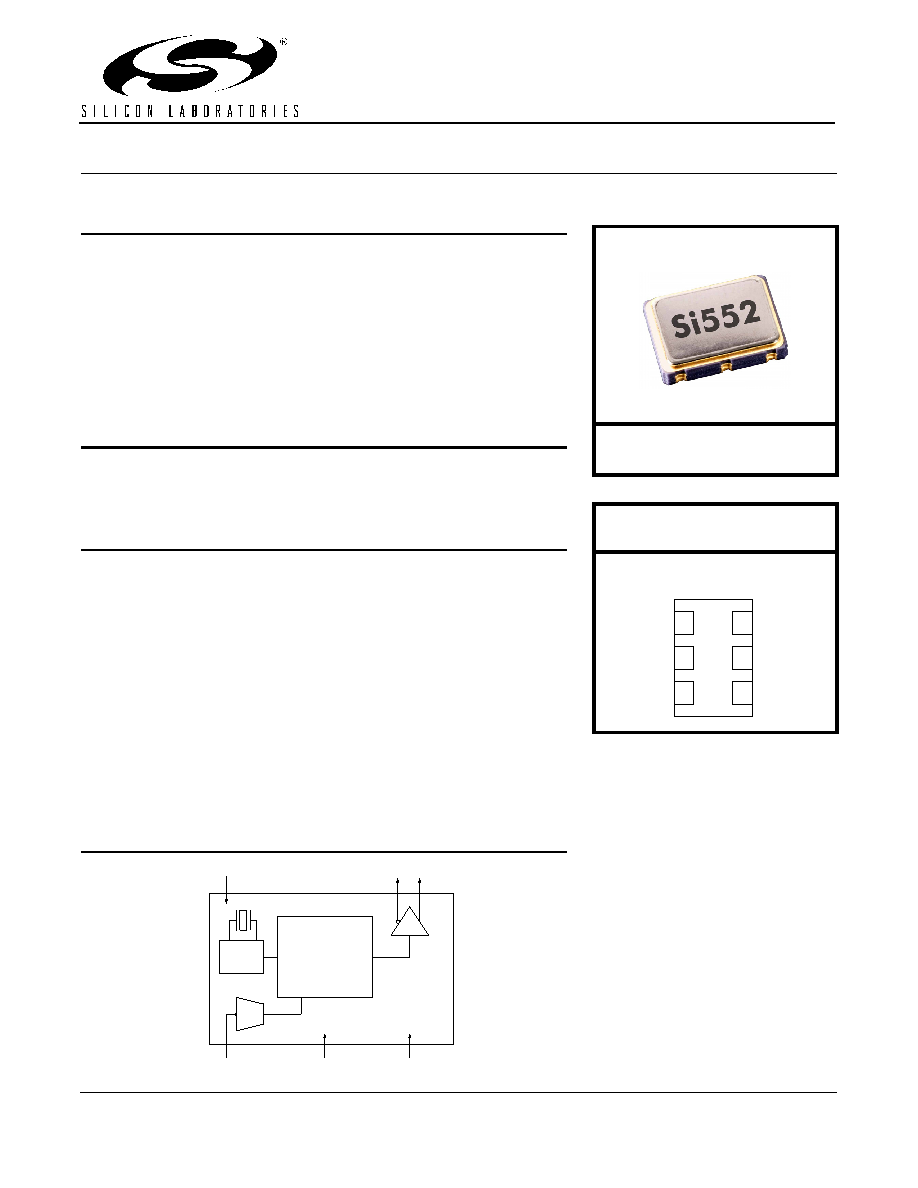

Si552

DUAL FREQUENCY VCXO (10 MHZ TO 1.4 GHZ)

Features

Applications

Description

The Si552 dual frequency VCXO utilizes Silicon Laboratories advanced

DSPLL circuitry to provide a very low jitter clock for all output frequencies.

The Si552 is available with any-rate output frequency from 10 to 945 MHz

and select frequencies to 1400 MHz. Unlike traditional VCXO’s where a

different crystal is required for each output frequency, the Si552 uses one

fixed crystal frequency to provide a wide range of output frequencies. This

IC based approach allows the crystal resonator to provide exceptional

frequency stability and reliability. In addition, DSPLL clock synthesis

provides superior supply noise rejection, simplifying the task of generating

low jitter clocks in noisy environments typically found in communication

systems. The Si552 IC based VCXO is factory configurable for a wide

variety of user specifications including frequency, supply voltage, output

format, tuning slope, and temperature stability. Specific configurations are

factory programmed at time of shipment, thereby eliminating long lead times

associated with custom oscillators.

Functional Block Diagram

Available with any-rate output

frequencies from 10–945 MHz and

select frequencies to 1.4 GHz

Two selectable output frequencies

3rd generation DSPLL with superior

jitter performance

3x better frequency stability than

SAW-based oscillators

Internal fixed crystal frequency

ensures high reliability and low

aging

Available CMOS, LVPECL, LVDS

& CML outputs

3.3, 2.5, and 1.8 V supply options

Industry-standard 5 x 7 mm

package and pinout

Pb-free/RoHS-compliant

SONET/SDH

xDSL

10 GbE LAN / WAN

Low-jitter clock generation

Optical Modules

Clock and data recovery

Fixed

Frequency XO

Any-rate

10–1400 MHz

DSPLL

Clock Synthesis

VDD

CLK+

CLK-

VC

GND

FS

ADC

Ordering Information:

See page 7.

Pin Assignments:

See page 6.

(Top View)

Si5602

1

2

3

6

5

4

VC

GND

FS

VDD

CLK+

CLK–

相關PDF資料 |

PDF描述 |

|---|---|

| 552AD000249BGR | VCXO, CLOCK, 173.37075 MHz, LVPECL OUTPUT |

| 550AC644M531BGR | VCXO, CLOCK, 644.531 MHz, LVPECL OUTPUT |

| 554QF000261BGR | VCXO, CLOCK, 172.6423 MHz, CMOS/TTL OUTPUT |

| 550AE625M000BG | VCXO, CLOCK, 625 MHz, LVPECL OUTPUT |

| 550AF27M0000BG | VCXO, CLOCK, 27 MHz, LVPECL OUTPUT |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 552AD000112DG | 制造商:Silicon Laboratories Inc 功能描述:CNTRLD OSC 622.08MHZ/644.53125MHZ VCXO LVPECL 6PIN - Trays |

| 552AD000112DGR | 制造商:Silicon Laboratories Inc 功能描述:CNTRLD OSC 622.08MHZ/644.53125MHZ VCXO LVPECL 6PIN - Tape and Reel |

| 552AD000116DG | 制造商:Silicon Laboratories Inc 功能描述:CNTRLD OSC 622.08MHZ/669.32658MHZ VCXO LVPECL 6PIN - Trays |

| 552AD000116DGR | 制造商:Silicon Laboratories Inc 功能描述:CNTRLD OSC 622.08MHZ/669.32658MHZ VCXO LVPECL 6PIN - Tape and Reel |

| 552AD000123DG | 制造商:Silicon Laboratories Inc 功能描述: |

發布緊急采購,3分鐘左右您將得到回復。