- 您現在的位置:買賣IC網 > PDF目錄68811 > 71M6532F-IGTR/F (MAXIM INTEGRATED PRODUCTS INC) 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 PDF資料下載

參數資料

| 型號: | 71M6532F-IGTR/F |

| 廠商: | MAXIM INTEGRATED PRODUCTS INC |

| 元件分類: | 電源管理 |

| 英文描述: | 1-CHANNEL POWER SUPPLY MANAGEMENT CKT, PQFP100 |

| 封裝: | LEAD FREE, LQFP-100 |

| 文件頁數: | 72/120頁 |

| 文件大小: | 2477K |

| 代理商: | 71M6532F-IGTR/F |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁當前第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁

FDS 6531/6532 005

Data Sheet 71M6531D/F-71M6532D/F

v1.3

2005-2010 TERIDIAN Semiconductor Corporation

55

2.2

System Timing Summary

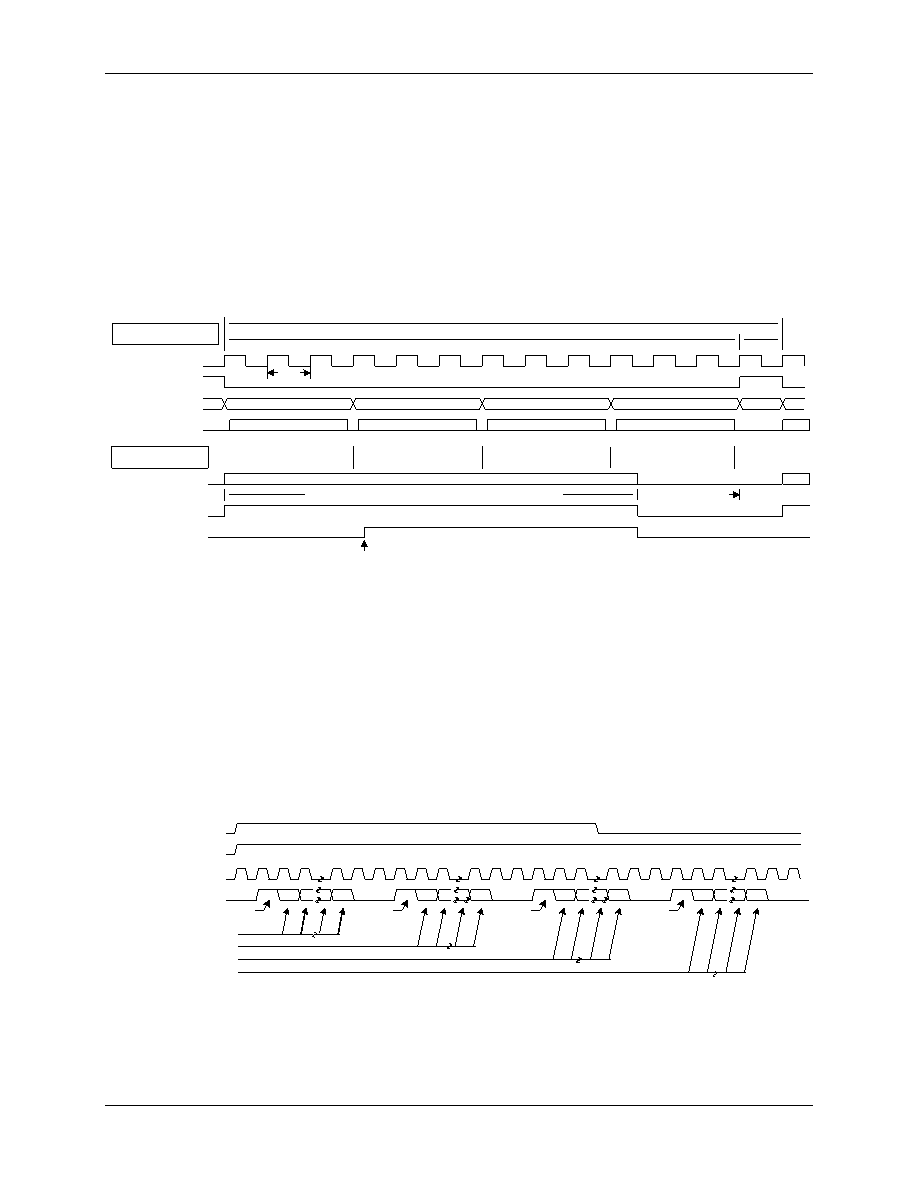

Figure 19 summarizes the timing relationships between the input MUX states, the CE_BUSY signal and

the two serial output streams. In this example, MUX_DIV[3:0] = 4 and FIR_LEN[1:0] = 2 (384 CE cycles,

3 CK32 cycles per conversion), resulting in 13 CK32 cycles per multiplexer frame. Generally, the duration

of each MUX frame is:

1 + MUX_DIV * 1, if FIR_LEN[1:0] = 0 (138 CE cycles)

1 + MUX_DIV * 2, if FIR_LEN[1:0] = 1 (288 CE cycles)

1 + MUX_DIV * 3, if FIR_LEN[1:0] = 2 (384 CE cycles).

An ADC conversion will always consume an integer number of CK32 clocks. Following this is a single

CK32 cycle where the bandgap voltage is allowed to recover from the change in CROSS.

Figure 19: Timing Relationship between ADC MUX, Compute Engine

Each CE program pass begins when the ADC0 conversion (for IA) begins. Depending on the length of

the CE program, it may continue running until the end of the last conversion (ADC3). CE opcodes are

constructed to ensure that all CE code passes consume exactly the same number of cycles. The result of

each ADC conversion is inserted into the RAM when the conversion is complete. The CE code is written

to tolerate sudden changes in ADC data. The exact clock count when each ADC value is loaded into

RAM is shown in Figure 19.

Figure 20 shows that the serial data stream, RTM, begins transmitting at the beginning of state S. RTM,

consisting of 140 CK cycles, will always finish before the next code pass starts.

FLAG

RTM DATA 0 (32 bits)

0

1

0

1

0

1

0

1

FLAG

CK32

MUX_SYNC

CKTEST

TMUXOUT/RTM

LSB

SIGN

LSB

SIGN

30

31

30

31

30

31

30

31

LSB

SIGN

RTM DATA 1 (32 bits)

RTM DATA 2 (32 bits)

RTM DATA 3 (32 bits)

Figure 20: RTM Output Format

CK32

MUX STATE

0

MUX_DIV=4 (4 conversions) is shown

Settle

ADC MUX Frame

ADC EXECUTION

S

MUX_SYNC

S

CE_EXECUTION

MAX CK COUNT

0

450

150

900

1350

1800

ADC0

ADC1

ADC2

ADC3

CK COUNT = CE_CYCLES + floor((CE_CYCLES + 2) / 5)

NOTES:

1. ALL DIMENSIONS ARE 5MHZ CK COUNTS.

2. THE PRECISE FREQUENCY OF CK IS 150*CRYSTAL FREQUENCY = 4.9152MHz.

3. XFER_BUSY OCCURS ONCE EVERY (PRE_SAMPS * SUM_CYCLES) CODE PASSES.

CE_BUSY

XFER_BUSY

INITIATED BY A CE OPCODE AT END OF SUMMATION INTERVAL

ADC TIMING

CE TIMING

1

2

3

相關PDF資料 |

PDF描述 |

|---|---|

| 71M6534-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6534H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6533H-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP100 |

| 71M6534-IGTR/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

| 71M6534H-IGT/F | SPECIALTY ANALOG CIRCUIT, PQFP120 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 71M6533 | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:Energy Meter IC |

| 71M6533-DB | 功能描述:開發板和工具包 - 8051 71M6533 Demo Brd RoHS:否 制造商:Silicon Labs 產品:Development Kits 工具用于評估:C8051F960, Si7005 核心: 接口類型:USB 工作電源電壓: |

| 71M6533G | 制造商:MAXIM 制造商全稱:Maxim Integrated Products 功能描述:Exceeds IEC 62053/ANSI C12.20 Standards |

| 71M6533G-IGTR/F | 功能描述:計量片上系統 - SoC AC Power Monitoring SoC-Programd RoHS:否 制造商:Maxim Integrated 核心:80515 MPU 處理器系列:71M6511 類型:Metering SoC 最大時鐘頻率:70 Hz 程序存儲器大小:64 KB 數據 RAM 大小:7 KB 接口類型:UART 可編程輸入/輸出端數量:12 片上 ADC: 安裝風格:SMD/SMT 封裝 / 箱體:LQFP-64 封裝:Reel |

| 71M6533H | 制造商:TERIDIAN 制造商全稱:TERIDIAN 功能描述:Energy Meter IC |

發布緊急采購,3分鐘左右您將得到回復。