- 您現在的位置:買賣IC網 > PDF目錄360445 > 74F8963 (NXP Semiconductors N.V.) 9-Bit latched bidirectional Futurebus transceivers open-collector PDF資料下載

參數資料

| 型號: | 74F8963 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 9-Bit latched bidirectional Futurebus transceivers open-collector |

| 中文描述: | 9位鎖存雙向Futurebus收發(fā)器集電極開路 |

| 文件頁數: | 1/10頁 |

| 文件大小: | 97K |

| 代理商: | 74F8963 |

Philips Semiconductors FAST Products

Product specification

74F8962/8963

9-Bit latched bidirectional Futurebus transceivers

(open-collector)

1

March 11, 1993

853–1425 09230

FEATURES

Octal latched transceiver

Drives heavily loaded backplanes with

equivalent load impedances down to 10

High drive (100mA) open collector drivers

on B port

Reduced voltage swing (1 volt) produces

less noise and reduces power consumption

High speed operation enhances

performance of backplane buses and

facilitates incident wave switching

Compatible with IEEE 896 futurebus

standards

Built–in precision band–gap reference

provides accurate receiver thresholds and

improved noise immunity

Multiple GND pins minimize ground bounce

Glitch–free power up/power down

operation

DESCRIPTION

The 74F8962 and 74F8963 are octal

bidirectional latched transceivers and are

intended to provide the electrical interface to

a high performance wired-OR bus. The B port

inverting drivers are low-capacitance open

collector with controlled ramp and are

designed to sink 100mA from 2 volts. The B

port inverting receivers have a 150mV

threshold region.

The B port interfaces to ‘Backplane

Transceiver Logic’ (BTL). BTL features a

reduced (1V to 2V) voltage swing for lower

power consumption and a series diode on

the drivers to reduce capacitive loading.

Incident wave switching to 9

is guaranteed.

The voltage swing is much less for BTL, so is

its receiver threshold region, therefore noise

margins are excellent.

BTL offers low power consumption, low

ground bounce, EMI and crosstalk, low

capacitive loading, superior noise margin and

low propagation delays. This results in a high

bandwidth, reliable backplane.

The 74F8962 and 74F8963 A ports have TTL

3-state drivers and TTL receivers with a latch

function.

The 74F8963 is the non-inverting version of

74F8962.

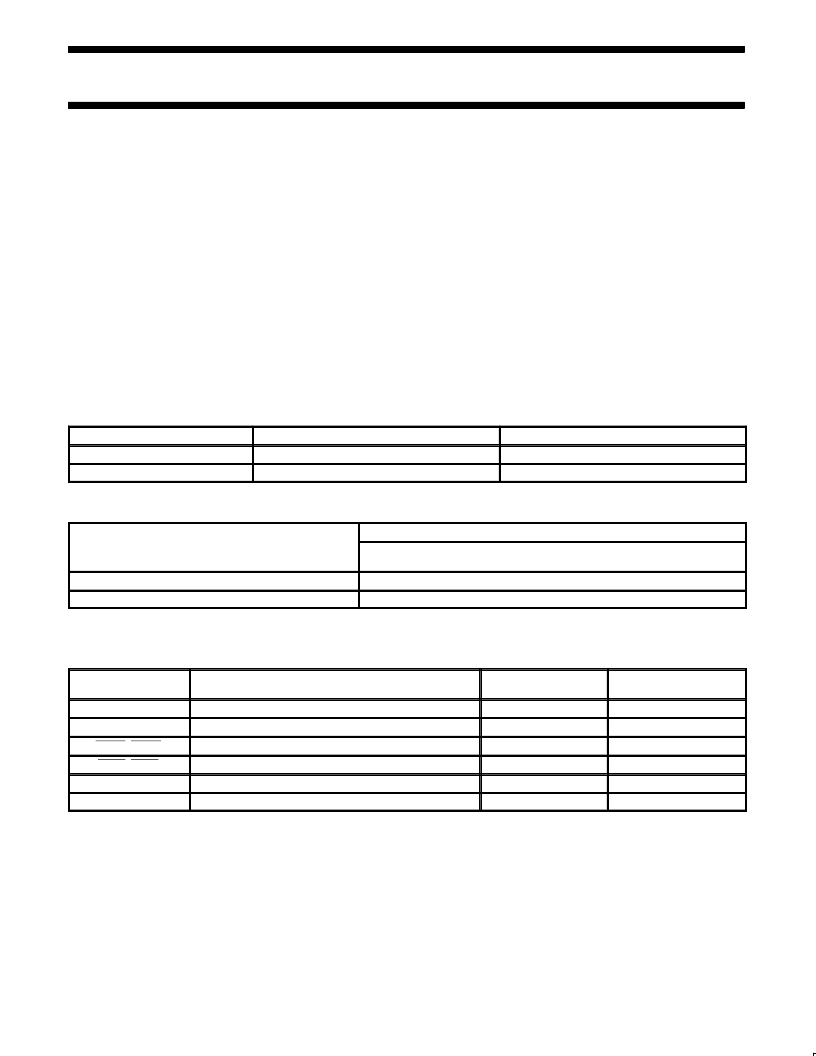

TYPE

TYPICAL PROPAGATION DELAY

TYPICAL SUPPLY CURRENT( TOTAL)

74F8962

6.5ns

90mA

74F8963

5.5ns

90mA

ORDERING INFORMATION

ORDER CODE

COMMERCIAL RANGE

V

CC

= 5V

±

10%, T

amb

= 0

°

C to +70

°

C

N74F8962Y, N74F8963Y

DESCRIPTION

44–pin Quad Flat Pack

1

44–pin Plastic Leaded Chip Carrier

Note to ordering information

1. Flatpack package is not available at this time.

N74F8962A, N74F8963A

INPUT AND OUTPUT LOADING AND FAN OUT TABLE

PINS

DESCRIPTION

74F (U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

AI0 – AI8

PNP latched inputs

1.0/0.167

20

μ

A/100

μ

A

100

μ

A/100

μ

A

20

μ

A/20

μ

A

20

μ

A/20

μ

A

B0 – B8

Data inputs with threshold circuitry

5.0/0.167

OEAB, OEBA

Output enable inputs (active low)

1.0/0.033

LEAB, LEBA

Latch enable inputs (active low)

1.0/0.033

AO0 – AO8

3–state outputs

150/40

3mA/24mA

B0 – B8

Open collector outputs

OC/166.7

OC/100mA

Notes to input and output loading and fan out table

1. One (1.0) FAST unit load is defined as: 20

μ

A in the high state and 0.6mA in the low state.

2. OC = Open collector.

相關PDF資料 |

PDF描述 |

|---|---|

| 74F8965 | 9-Bit address/data Futurebus transceiver, ADT |

| 74F8966 | 9-Bit address/data Futurebus transceiver, ADT |

| 74F978PC | Octal D-Type Flip-Flop |

| 74F978QC | Octal D-Type Flip-Flop |

| 74F978SC | Octal D-Type Flip-Flop |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 74F8965 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:9-Bit address/data Futurebus transceiver, ADT |

| 74F8966 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:9-Bit address/data Futurebus transceiver, ADT |

| 74F899 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:9-Bit Latchable Transceiver with Parity Generator/Checker |

| 74F899_YCB3026T WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

| 74F899_YCC3026B WAF | 制造商:Fairchild Semiconductor Corporation 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。