- 您現在的位置:買賣IC網 > PDF目錄24617 > 9161A-01CW16WLF (INTEGRATED DEVICE TECHNOLOGY INC) 120 MHz, VIDEO CLOCK GENERATOR, PDSO16 PDF資料下載

參數資料

| 型號: | 9161A-01CW16WLF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產生/分配 |

| 英文描述: | 120 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| 封裝: | 0.300 INCH, SOIC-16 |

| 文件頁數: | 12/15頁 |

| 文件大小: | 539K |

| 代理商: | 9161A-01CW16WLF |

6

ICS9161A

The serial data register is exactly 24 bits long, enough to

accept the data being sent. The stop bit acts as a load command

that passes the contents of the Serial Data Register into the

register indicated by the three address bits. If a stop bit is not

received after the serial register is full, and more data is sent,

all data in the register is ignored and an error issued. If correct

data is received, then the unlocking mechanism re-arms, all

data in the serial data register is ignored, and an error is

issued.

ERROUT# Operation

Any error in programming the ICS9161A is signaled by

ERROUT#. When the pin goes low, an error has been detected.

It stays low until the next unlock sequence. The signal is

invoked for any of the following errors: incorrect start bit,

incorrect data encoding, incorrect length of data word, and

incorrect stop bit.

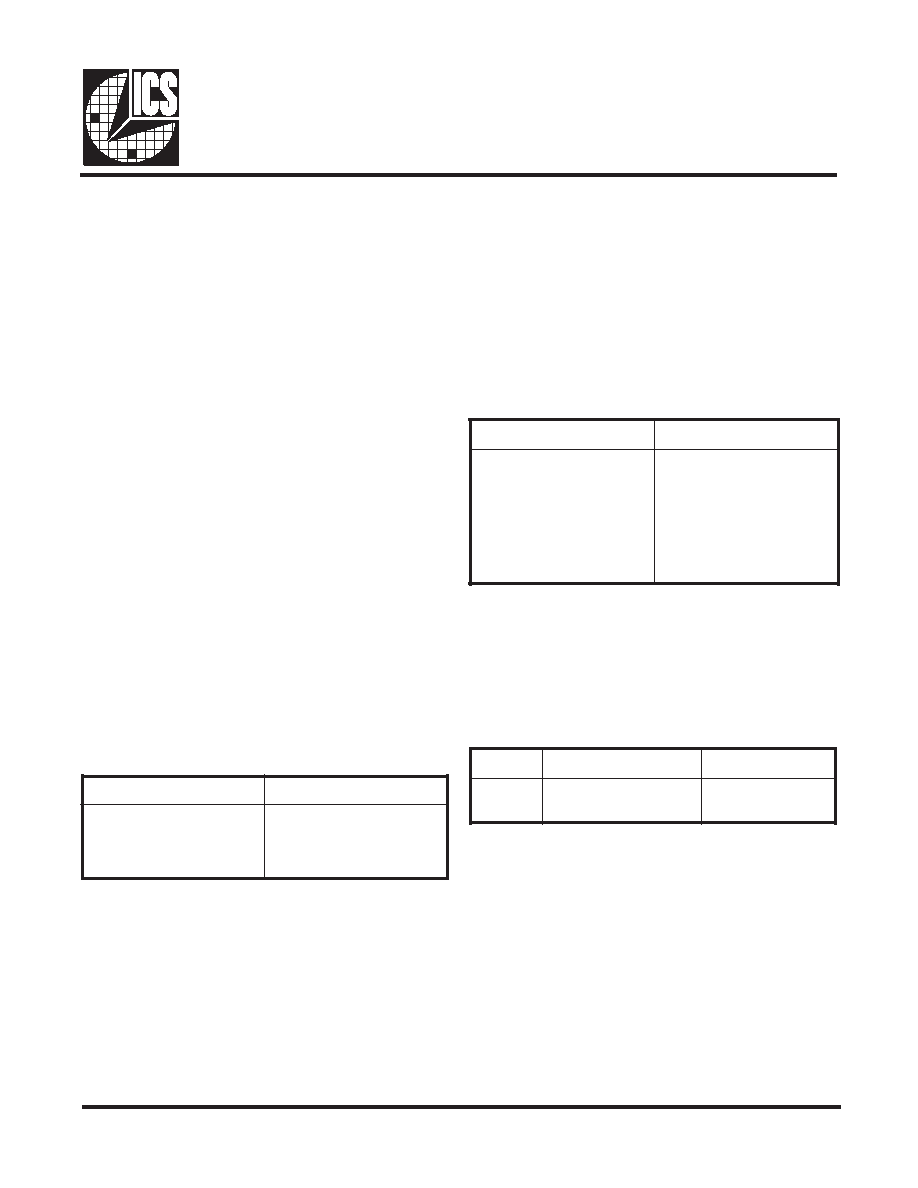

Programming the ICS9161A

The ICS9161A has a wide operating range, but it is

recommended that it is operated within the following limits:

3.15V< VDD <5.25V

VDD supply voltage

1 MHz <FREF <60 MHz

FREF=Input Reference

Frequency

200 kHz <FREF/M <5 MHz

M=Reference divide 3

to 129

50 MHz < FVCO <120 MHz

FVCO=VCO output

frequency

FCLK 120 MHz

FCLK=output frequency

The frequency of the programmable oscillator FVCO is

determined by the following fields:

The equations used to determine the oscillator frequency are:

N=N + 3 M=M + 2

FVCO=Prescale N/M FREF

where 3 M 129 and 4 N 130

and prescale=2 or 4, as set in the control register

(Where N is the VCO divider & M is the reference divider)

The value of FVCO must remain between 50 MHz and 120 MHz.

As a result, for output frequencies below 50 MHz, FVCO must

be brought into range. To achieve this, an output divisor is

selected by setting the values of the Mux Field (R) as follows:

Where the least significant bit is the last bit of M and the most

significant bit is the first bit of I.

Output Divisor

Unlike the ICD2061A, the ICS9161As VCO does not

require tuning to place it in certain ranges. The ICS9161As

VCO will operate from 50 MHz to 120 MHz without adjusting

the VCO gain. However, to maintain compatibility, the I bits

are programmed as in the ICD2061A.

These bits are dummy bits except for the following two cases:

Index Field (I)

When the index field is set to 1111, VCLK is turned off and

both channels run from the same MCLK VCO. This is done in

an effort to reduce jitter, which may increase when VCOs run

at 2n multiples of one another. If the two outputs have to be

multiples of one another, it is best to mux MCLK over to the

output of the VCLK VCO and to power-down the VCLK VCO.

The multiplexed frequency will be divided down by the correct

divisor (M) and output on VCLK.

d

l

e

i

Fs

t

i

B

f

o

#

)

I

(

x

e

d

n

I

)

'

N

(

e

u

l

a

v

r

e

t

n

u

o

c

N

)

R

(

x

u

M

)

'

M

(

e

u

l

a

v

r

e

t

n

u

o

c

M

4

7

3

7

Rr

o

s

i

v

i

D

0

1

0

1

0

1

0

1

0

1

0

1

2

4

8

6

1

2

3

4

6

8

2

1

IF

K

L

C

V

O

C

V

F

K

L

C

M

O

C

V

0

1

K

L

C

V

f

o

n

r

u

T

K

C

L

V

o

t

K

L

C

M

x

u

M

z

H

M

0

2

1

-

0

5

z

H

M

0

2

1

-

0

5

相關PDF資料 |

PDF描述 |

|---|---|

| 9161A-01CW16W | 120 MHz, VIDEO CLOCK GENERATOR, PDSO16 |

| 9162C | 2M X 32 FAST PAGE DRAM MODULE, 60 ns, SMA72 |

| 9163901MFA | QUAD LINE DRIVER, CDFP16 |

| 9163901MEA | QUAD LINE DRIVER, CDIP16 |

| 9163901M2A | QUAD LINE DRIVER, CQCC20 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 9-161A-R | 制造商:Cinch Connectors 功能描述: |

| 9161-CHR-BULK | 制造商:Belden Inc 功能描述: |

| 9-161-L | 制造商:Cinch Connectors 功能描述: |

| 9-161-R | 制造商:Cinch Connectors 功能描述:Conn Terminal Strip 9 POS 11.13mm Crimp ST Cable Mount |

| 9162 | 功能描述:PROTO-BOARD 14/16PIN SOIC SMD RoHS:是 類別:原型開發產品 >> 適配器,可互換接口板 系列:9000, Surfboards® 標準包裝:1 系列:- 原型板類型:- Package Accepted:- 尺寸/尺寸:- 位置數:- 孔直徑:- 板厚度:- 材質:- |

發布緊急采購,3分鐘左右您將得到回復。