- 您現在的位置:買賣IC網 > PDF目錄36336 > 935261221118 (NXP SEMICONDUCTORS) SPECIALTY CONSUMER CIRCUIT, PDSO28 PDF資料下載

參數資料

| 型號: | 935261221118 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 消費家電 |

| 英文描述: | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 封裝: | PLASTIC, SOT-341, SSOP-28 |

| 文件頁數: | 9/44頁 |

| 文件大小: | 241K |

| 代理商: | 935261221118 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁當前第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁

2000 Jan 24

17

Philips Semiconductors

Product specication

5 V mixers/oscillators and synthesizers for

cable TV and VCR 2-band tuners

TDA6402; TDA6402A;

TDA6403; TDA6403A

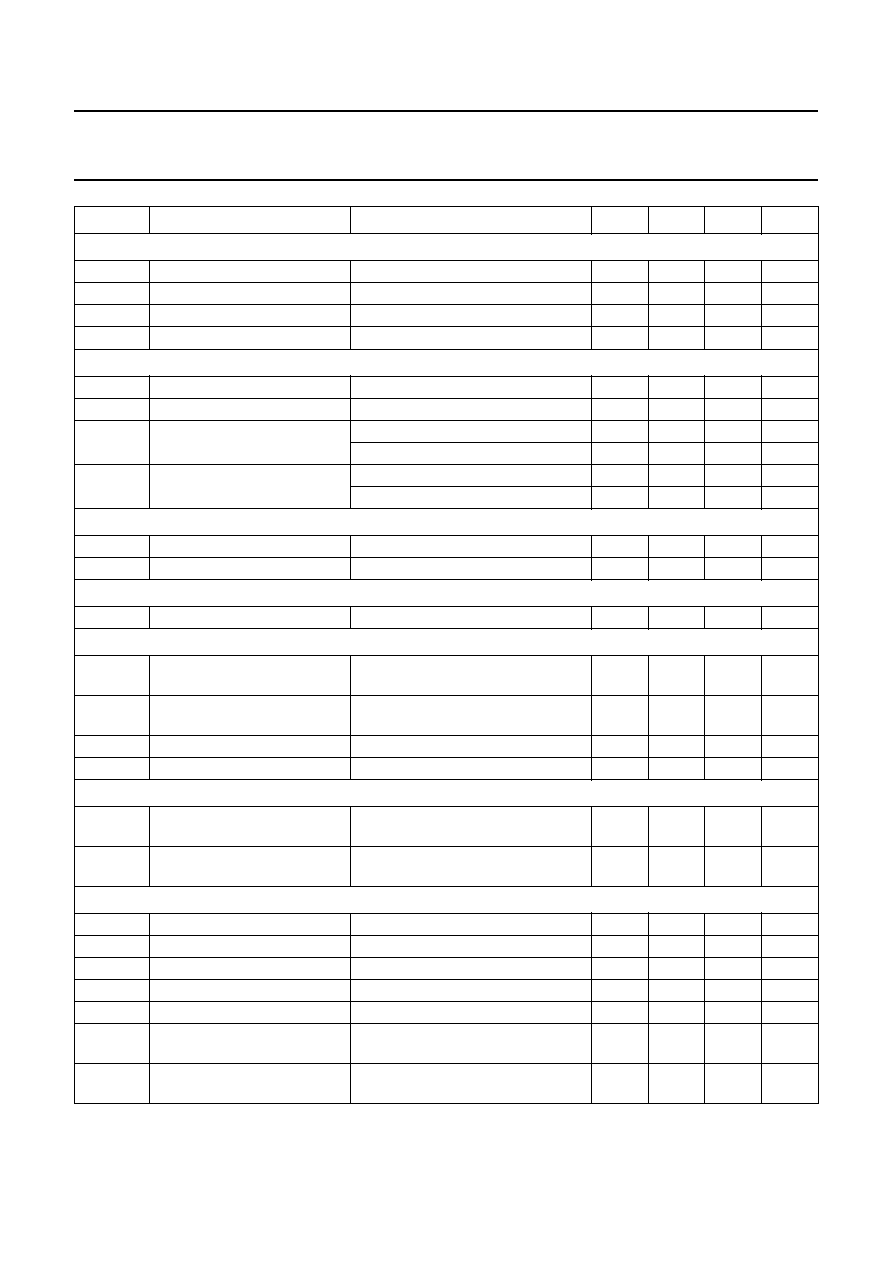

CE/AS INPUT (CHIP ENABLE/ADDRESS SELECTION)

VCE/ASL

LOW-level input voltage

0

1.5

V

VCE/ASH

HIGH-level input voltage

3

5.5

V

ICE/ASH

HIGH-level input current

VCE/AS = 5.5 V

10

A

ICE/ASL

LOW-level input current

VCE/AS =0V

10

A

CL AND DA INPUTS

VCL/DAL

LOW-level input voltage

0

1.5

V

VCL/DAH

HIGH-level input voltage

3

5.5

V

ICL/DAH

HIGH-level input current

VBUS = 5.5 V; VCC =0V

10

A

VBUS = 5.5 V; VCC = 5.5 V

10

A

ICL/DAL

LOW-level input current

VBUS = 1.5 V; VCC =0V

10

A

VBUS =0V; VCC = 5.5 V

10

A

DA OUTPUT (I2C-BUS MODE)

IDAH

leakage current

VDA = 5.5 V

10

A

VDA

output voltage

IDA = 3 mA (sink current)

0.4

V

CLOCK FREQUENCY

fclk

clock frequency

100

150

kHz

CHARGE PUMP OUTPUT CP

ICPH

HIGH-level input current

(absolute value)

CP = 1

280

A

ICPL

LOW-level input current

(absolute value)

CP = 0

60

A

VCP

output voltage

PLL is locked; Tamb =25 °C

1.95

V

ICPleak

off-state leakage current

T2 = 0; T1 = 1

15

0.5

+15

nA

TUNING VOLTAGE OUTPUT VT

IVTOFF

leakage current when

switched off

OS = 1; tuning supply = 33 V

10

A

VVT

output voltage when the loop

is closed

OS = 0; T2 = 0; T1 = 0; T0 = 1;

RLOAD =22k; tuning supply = 33 V

0.2

32.7

V

3-WIRE BUS TIMING

tHIGH

clock HIGH time

see Fig.7

2

s

tSU;DA

data set-up time

see Fig.7

2

s

tHD;DA

data hold time

see Fig.7

2

s

tSU;ENCL

enable to clock set-up time

see Fig.7

10

s

tHD;ENDA

enable to data hold time

see Fig.7

2

s

tEN

enable time between two

transmissions

see Fig.8

10

s

tHD;ENCL

enable to clock active edge

hold time

see Fig.8

6

s

SYMBOL

PARAMETER

CONDITIONS

MIN.

TYP.

MAX.

UNIT

相關PDF資料 |

PDF描述 |

|---|---|

| 935261221512 | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 935261221518 | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 935261234112 | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 935261234118 | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

| 935261234512 | SPECIALTY CONSUMER CIRCUIT, PDSO28 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 935262025112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935262217118 | 制造商:NXP Semiconductors 功能描述:Real Time Clock Serial 8-Pin SO T/R |

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

發布緊急采購,3分鐘左右您將得到回復。