- 您現在的位置:買賣IC網 > PDF目錄36338 > 935262255557 (NXP SEMICONDUCTORS) 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 PDF資料下載

參數資料

| 型號: | 935262255557 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | ADC |

| 英文描述: | 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| 封裝: | PLASTIC, SOT-317-2, QFP-64 |

| 文件頁數: | 11/40頁 |

| 文件大小: | 250K |

| 代理商: | 935262255557 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁

1999 Feb 24

19

Philips Semiconductors

Product specication

Triple high-speed Analog-to-Digital

Converter (ADC)

TDA8752A

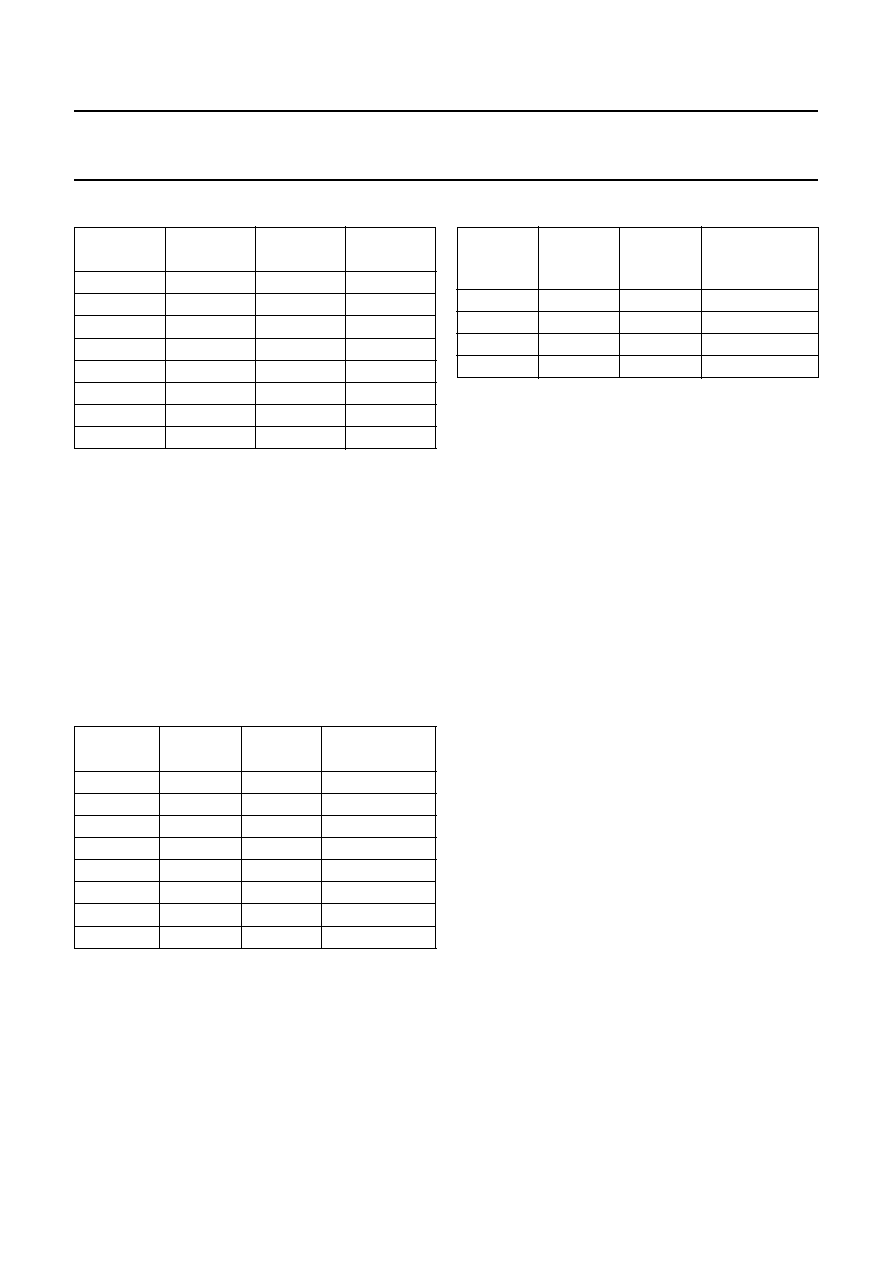

Table 5

Charge-pump current control

The default programmed value is as follows:

Charge pump current = 100 A

Test bits: no test mode; bits Up and Do at logic 0

Rising edge of CKREF: bit edge at logic 0

COAST and HSYNC inputs are active HIGH: V level and

H level at logic 0.

VCO REGISTER

The bits Z2, Z1 and Z0 enable the internal resistance for

the VCO filter to be selected.

Table 6

VCO register bits

Ip2

Ip1

Ip0

CURRENT

(

A)

0

6.25

0

1

12.5

010

25

011

50

100

101

200

110

400

111

700

Z2

Z1

Z0

RESISTANCE

(k

)

0

high impedance

0

1

128

01

0

32

01

1

16

10

0

8

10

1

4

11

0

2

11

1

Table 7

VCO gain control

The bits VCO1 and VCO0 control the VCO gain.

The default programmed value is as follows:

Internal resistance = 16 k

VCO gain = 15 MHz/V.

DIVIDER REGISTER

This register controls the PLL frequency. The bits are the

LSB bits.

The default programmed value is 0011 0010 0000 = 800.

The MSB bits (Di11, Di10 and Di9) and the LSB bit (Di0)

have to be programmed before the bits Di8 to Di1 to have

the required divider ratio. The bit Di0 is used for the parity

divider number = Di0 = 0 = even number Di0 = 1 = odd

number. It should be noted that if the I2C-bus programming

is done in mode = 1 and the bit Di0 has to be toggled, then

the registers have to be loaded twice to have the update

divider ratio.

POWER-DOWN MODE

When the supply is completely switched off, the

registers are set to their default values; in that event they

have to be reprogrammed if the required settings are

different (e.g. through an EEPROM)

When the device is in power-down mode, the previously

programmed register values remain unaffected.

PHASEA AND PHASEB REGISTERS

The bit Cka is logic 0 when the used clock is the PLL clock,

and logic 1 when the used clock is the external clock.

The bit Ckb is logic 0 when the second clock is not used.

The bits Pa4 to Pa0 and Pb4 to Pb0 are used to program

the phase shift for the clock, CKADCO, CKAO and CKBO

(see Table 8).

VCO1

VCO0

VCO gain

(MHz/V)

PIXEL CLOCK

FREQUENCY

RANGE (MHz)

1

0

60

10 to 17

0

1

30

17 to 35

1

0

60

35 to 60

1

100

60 to 100

相關PDF資料 |

PDF描述 |

|---|---|

| 935266896551 | 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| 935266896557 | 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| 935262255551 | 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| 935262254557 | 3-CH 8-BIT PROPRIETARY METHOD ADC, PARALLEL ACCESS, PQFP100 |

| 935262318518 | COLOR SIGNAL ENCODER, PQFP44 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

| 935268081112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935268721125 | 制造商:NXP Semiconductors 功能描述:Buffer/Line Driver 1-CH Non-Inverting 3-ST CMOS 5-Pin TSSOP T/R |

| 935269304128 | 制造商:ST-Ericsson 功能描述:IC AUDIO CODEC W/TCH SCRN 48LQFP |

發布緊急采購,3分鐘左右您將得到回復。