- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄164924 > 9704-01 (PEREGRINE SEMICONDUCTOR CORP) 3.0 GHz Integer-N PLL for Rad Hard Apllications PDF資料下載

參數(shù)資料

| 型號: | 9704-01 |

| 廠商: | PEREGRINE SEMICONDUCTOR CORP |

| 元件分類: | PLL合成/DDS/VCOs |

| 英文描述: | 3.0 GHz Integer-N PLL for Rad Hard Apllications |

| 中文描述: | PHASE LOCKED LOOP, CQCC44 |

| 封裝: | CERAMIC, QFJ-44 |

| 文件頁數(shù): | 4/10頁 |

| 文件大小: | 247K |

| 代理商: | 9704-01 |

Product Specification

PE9704

Page 3 of 10

Document No. 70-0083-03

│ www.psemi.com

2003-2006 Peregrine Semiconductor Corp. All rights reserved.

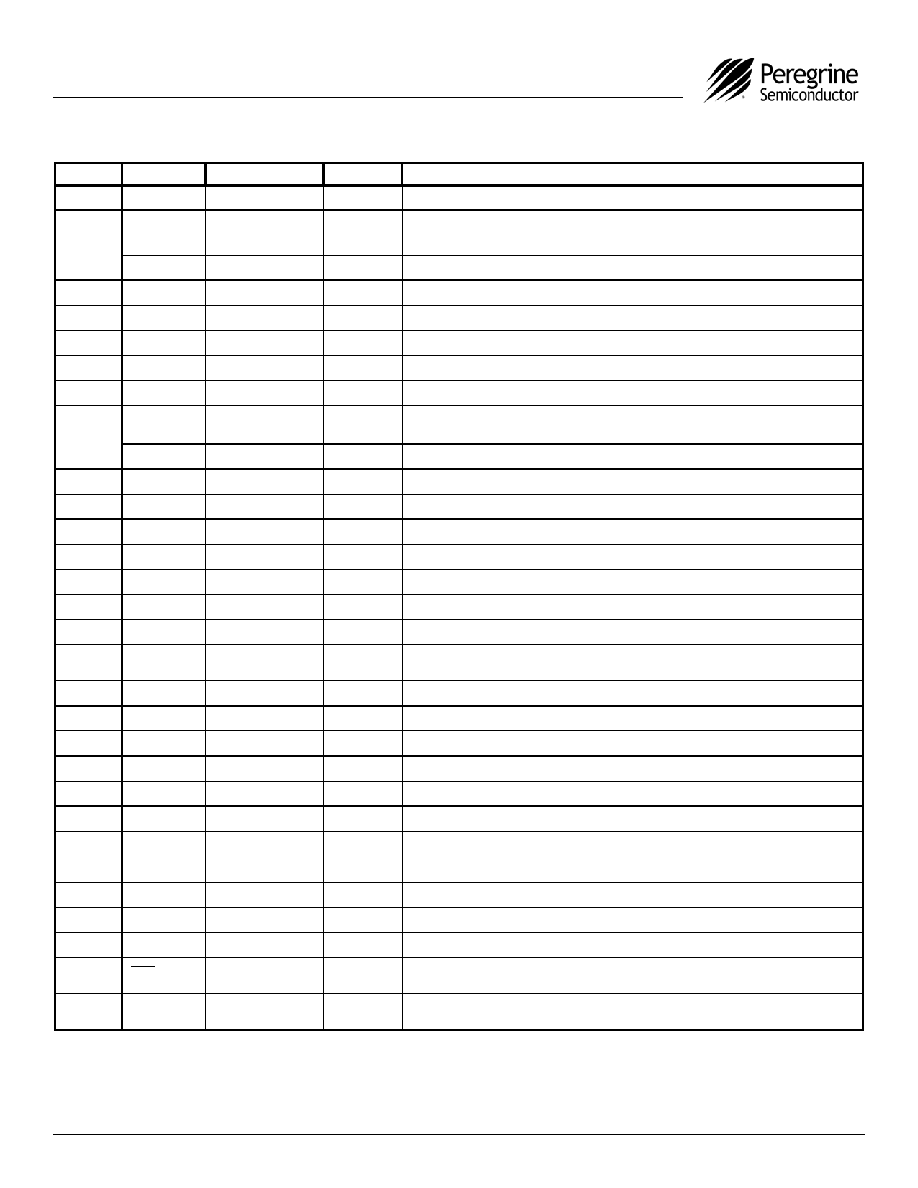

Table 1. Pin Descriptions (continued)

17

GND

Both

Ground

18

CLOCK

Serial

Input

Clock input. Data is clocked serially into either the 20-bit primary register (E_WR

“l(fā)ow”) or the 8-bit enhancement register (E_WR “high”) on the rising edge of

CLOCK.

M6

Direct

Input

M Counter bit6

19

M7

Direct

Input

M Counter bit7

20

M8

Direct

Input

M Counter bit8 (MSB)

21

A0

Direct

Input

A Counter bit0

22

DMODE

Both

Input

Selects direct interface mode (DMODE=1) or serial interface mode (DMODE=0)

23

VDD

Both

(Note 1)

Same as pin 1

24

E_WR

Serial

Input

Enhancement register write enable. While E_WR is “high”, DATA can be serially

clocked into the enhancement register on the rising edge of CLOCK.

A1

Direct

Input

A Counter bit1.

25

A2

Direct

Input

A Counter bit2

26

A3

Direct

Input

A Counter bit3 (MSB)

27

FIN

Both

Input

RF prescaler input from the VCO. 3.0 GHz maximum frequency.

28

GND

Both

Ground.

29

GND

Both

Ground.

30

N/C

No connect.

31

VDD

Both

(Note 1)

Same as pin 1

32

DOUT

Serial

Output

Data Out. The Main Counter output, R Counter output, or dual modulus prescaler

select (MSEL) can be routed to DOUT through enhancement register programming.

33

VDD

Both

(Note 1)

Same as pin 1

34

N/C

No connect.

35

GND

Both

Ground.

36

PD_

D

Both

Output

PD_

D pulses down when f

p leads fc.

37

PD_

U

Both

PD_

U pulses down when f

c leads fp.

38

VDD

Both

(Note 1)

Same as pin 1

39

CEXT

Both

Output

Logical “NAND” of PD_

U and PD_D, passed through an on-chip, 2 k series

resistor. Connecting CEXT to an external capacitor will low pass filter the input to the

inverting amplifier used for driving LD.

40

GND

Both

Ground

41

GND

Both

Ground

42

FR

Both

Input

Reference frequency input

43

ENH

Both

Output, OD

Enhancement mode. When asserted low (“0”), enhancement register bits are

functional.

44

LD

Serial

Output

Lock detect output, the open-drain logical inversion of CEXT. When the loop is

locked, LD is high impedance; otherwise LD is a logic low (“0”).

Note 1:

VDD pins 1, 11, 12, 23, 31, 33, 35, and 38 are connected by diodes and must be supplied with the same positive voltage level.

Note 2:

All digital input pins have 70 k

pull-down resistors to ground.

Pin No.

Pin Name

Interface Mode

Type

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9704-11 | 3.0 GHz Integer-N PLL for Rad Hard Apllications |

| 971-36006-21 | 36 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, PRESS FIT |

| 971-36006-31 | 36 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, PRESS FIT |

| 971-36009-21 | 36 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, PRESS FIT |

| 971-36009-31 | 36 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, PRESS FIT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9704-0159 | 功能描述:近程傳感器 IRAL-294-S5 - -2030VDC;50mA -NPN- -QD59-HSDO RoHS:否 制造商:Vishay Semiconductors 感應(yīng)方式:Optical 感應(yīng)距離:1 mm to 200 mm 電源電壓:2.5 V to 3.6 V 安裝風(fēng)格:SMD/SMT 輸出配置:Digital 最大工作溫度:+ 85 C 最小工作溫度:- 25 C 系列:VCNL3020 |

| 97-041.007 | 制造商:EAO International 功能描述:PCB INDICATOR SQUARE |

| 97041002 | 制造商:Laird Technologies Inc 功能描述:CSTR STR BF |

| 9704-11 | 制造商:PEREGRINE 制造商全稱:PEREGRINE 功能描述:3000 MHz UltraCMOS⑩ Integer-N PLL Rad Hard for Space Applications |

| 97042002 | 制造商:Laird Technologies Inc 功能描述:CSTR FRG BF |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。