- 您現在的位置:買賣IC網 > PDF目錄164924 > 9704-01 (PEREGRINE SEMICONDUCTOR CORP) 3.0 GHz Integer-N PLL for Rad Hard Apllications PDF資料下載

參數資料

| 型號: | 9704-01 |

| 廠商: | PEREGRINE SEMICONDUCTOR CORP |

| 元件分類: | PLL合成/DDS/VCOs |

| 英文描述: | 3.0 GHz Integer-N PLL for Rad Hard Apllications |

| 中文描述: | PHASE LOCKED LOOP, CQCC44 |

| 封裝: | CERAMIC, QFJ-44 |

| 文件頁數: | 9/10頁 |

| 文件大?。?/td> | 247K |

| 代理商: | 9704-01 |

Product Specification

PE9704

Page 8 of 10

2003-2006 Peregrine Semiconductor Corp. All rights reserved.

Document No. 70-0083-03

│ UltraCMOS RFIC Solutions

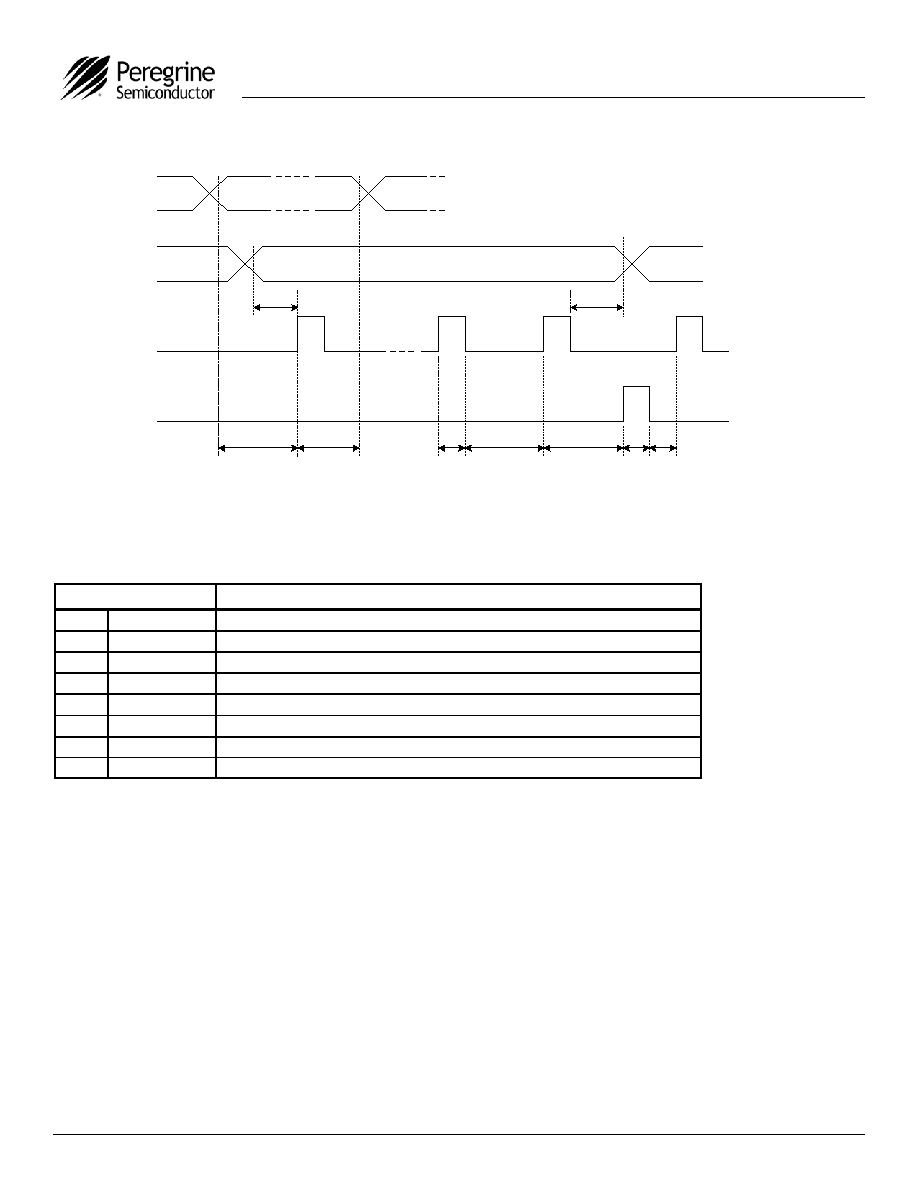

Figure 4. Serial Interface Mode Timing Diagram

t

DHLD

t

DSU

t

ClkH

t

ClkL

t

CWR

t

PW

t

WRC

t

EC

t

CE

E_WR

DATA

CLOCK

S_WR

PD_U pulses result in an increase in VCO

frequency and

PD_D results in a decrease in VCO

frequency.

Software tools for designing the active loop filter

can be found at Peregrine’s web site:

www.psemi.com

Lock Detect Output

A lock detect signal is provided at pin LD, via the

pin CEXT (see Figure 1). CEXT is the logical “NAND”

of PD_

U and PD_D waveforms, driven through a

series 2 k

resistor. Connecting C

EXT to an

external shunt capacitor provides integration of

this signal.

Enhancement Register

The functions of the enhancement register bits are shown below. All bits are active high. Operation is

undefined if more than one output is sent to DOUT.

Table 9. Enhancement Register Bit Functionality

** Program to 0

Phase Detector Outputs

The phase detector is triggered by rising edges

from the main counter (fp) and the reference

counter (fc). It has two outputs, PD_U, and PD_D.

If the divided VCO leads the divided reference in

phase or frequency (fp leads fc), PD_D pulses

“low”. If the divided reference leads the divided

VCO in phase or frequency (fc leads fp), PD_U

pulses “low”. The width of either pulse is directly

proportional to phase offset between the two input

signals, fp and fc. The phase detector gain is

430 mV / radian.

PD_U and PD_D are designed to drive an active

loop filter which controls the VCO tune voltage.

Bit Function

Description

Bit 0

Reserved**

Bit 1

Reserved**

Bit 2

fp output

Drives the M counter output onto the DOUT output.

Bit 3

Power down

Power down of all functions except programming interface.

Bit 4

Counter load

Immediate and continuous load of counter programming.

Bit 5

MSEL output

Drives the internal dual modulus prescaler modulus select (MSEL) onto the DOUT output.

Bit 6

fc output

Drives the R counter output onto the DOUT output

Bit 7

PB

Allows Fin to bypass the 10/11 prescaler

相關PDF資料 |

PDF描述 |

|---|---|

| 9704-11 | 3.0 GHz Integer-N PLL for Rad Hard Apllications |

| 971-36006-21 | 36 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, PRESS FIT |

| 971-36006-31 | 36 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, PRESS FIT |

| 971-36009-21 | 36 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, PRESS FIT |

| 971-36009-31 | 36 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, PRESS FIT |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 9704-0159 | 功能描述:近程傳感器 IRAL-294-S5 - -2030VDC;50mA -NPN- -QD59-HSDO RoHS:否 制造商:Vishay Semiconductors 感應方式:Optical 感應距離:1 mm to 200 mm 電源電壓:2.5 V to 3.6 V 安裝風格:SMD/SMT 輸出配置:Digital 最大工作溫度:+ 85 C 最小工作溫度:- 25 C 系列:VCNL3020 |

| 97-041.007 | 制造商:EAO International 功能描述:PCB INDICATOR SQUARE |

| 97041002 | 制造商:Laird Technologies Inc 功能描述:CSTR STR BF |

| 9704-11 | 制造商:PEREGRINE 制造商全稱:PEREGRINE 功能描述:3000 MHz UltraCMOS⑩ Integer-N PLL Rad Hard for Space Applications |

| 97042002 | 制造商:Laird Technologies Inc 功能描述:CSTR FRG BF |

發布緊急采購,3分鐘左右您將得到回復。