- 您現在的位置:買賣IC網 > PDF目錄25563 > 9DB106BFILFT (INTEGRATED DEVICE TECHNOLOGY INC) 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 PDF資料下載

參數資料

| 型號: | 9DB106BFILFT |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘及定時 |

| 英文描述: | 9DB SERIES, PLL BASED CLOCK DRIVER, 6 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO28 |

| 封裝: | 0.209 INCH, ROHS COMPLIANT, MO-150, SSOP-28 |

| 文件頁數: | 1/14頁 |

| 文件大小: | 152K |

| 代理商: | 9DB106BFILFT |

9DB106

IDT

Six Output Differential Buffer for PCIe Gen 2

9DB106

REV K 04/20/11

Six Output Differential Buffer for PCIe Gen 2

DATASHEET

1

SPREAD

COMPATIBLE

PLL

CONTROL

LOGIC

SMBDAT

SMBCLK

CLK_INT

C LK_INC

PLL_BW

IREF

PCIEX1

PCIEX4

CLKREQ4#

CLKREQ1#

PCIEX(0,2,3,5)

Description

Output Features

The 9DB106 zero-delay buffer supports PCIe Gen1 and Gen2

clocking requirements. The 9DB106 is driven by a differential SRC

output pair from an IDT CK410/CK505-compliant main clock

generator. It attenuates jitter on the input clock and has a selectable

PLL bandwidth to maximize performance in systems with or without

Spread-Spectrum clocking. An SMBus interface allows control of

the PLL bandwidth and bypass options, while 2 clock request

(CLKREQ#) pins make the 9DB106 suitable for Express Card

applications.

6 - 0.7V current mode differential output pairs (HSCL)

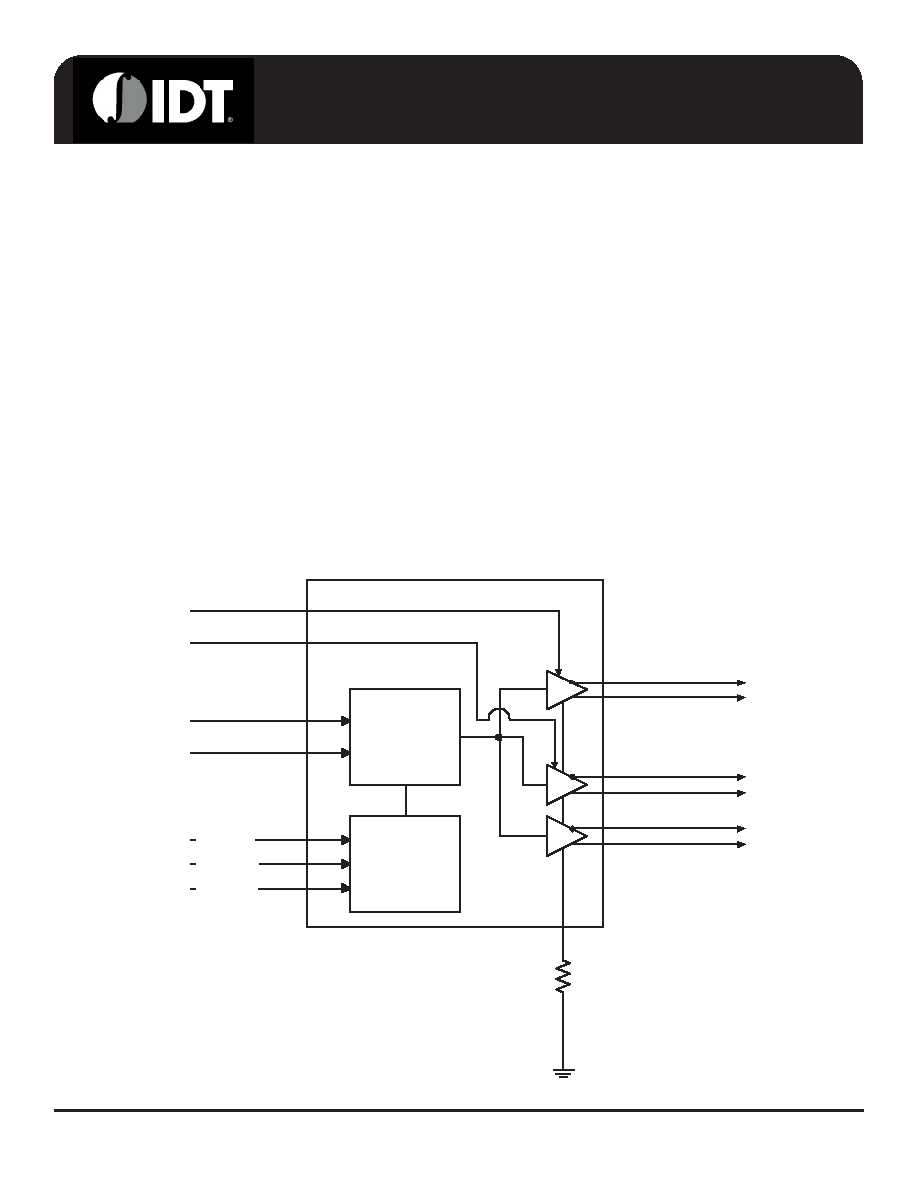

Functional Block Diagram

Key Specifications

Cycle-to-cycle jitter < 50ps

Output-to-output skew < 50 ps

Features/Benefits

CLKREQ# pin for outputs 1 and 4/ supports Express Card

applications

PLL or bypass mode/PLL can dejitter incoming clock

Selectable PLL bandwidth/minimizes jitter peaking in

downstream PLL's

Spread Spectrum Compatible/tracks spreading input clock

for low EMI

SMBus Interface/unused outputs can be disabled

Recommended Applications

6 Output Differential Buffer for PCIe Gen 2

相關PDF資料 |

PDF描述 |

|---|---|

| 9DB108BFLF | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB108BGLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB108BFLF-T | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB108YGLFT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

| 9DB108YGT | 9DB SERIES, PLL BASED CLOCK DRIVER, 8 TRUE OUTPUT(S), 0 INVERTED OUTPUT(S), PDSO48 |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 9DB106BFLF | 功能描述:時鐘緩沖器 6 OUTPUT PCIE GEN2 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB106BFLFT | 功能描述:時鐘緩沖器 6 OUTPUT PCIE GEN2 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB106BGILF | 功能描述:時鐘緩沖器 6 OUTPUT PCIE GEN2 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB106BGILFT | 功能描述:時鐘緩沖器 6 OUTPUT PCIE GEN2 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

| 9DB106BGLF | 功能描述:時鐘緩沖器 6 OUTPUT PCIE GEN2 BUFFER RoHS:否 制造商:Texas Instruments 輸出端數量:5 最大輸入頻率:40 MHz 傳播延遲(最大值): 電源電壓-最大:3.45 V 電源電壓-最小:2.375 V 最大功率耗散: 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:LLP-24 封裝:Reel |

發布緊急采購,3分鐘左右您將得到回復。