- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄164972 > A3PN125-Z2VQG100I FPGA, 3072 CLBS, 125000 GATES, PQFP100 PDF資料下載

參數(shù)資料

| 型號(hào): | A3PN125-Z2VQG100I |

| 元件分類: | FPGA |

| 英文描述: | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| 封裝: | 14 X 14 MM, 1.20 MM HEIGHT, 0.50 MM PITCH, ROHS COMPLIANT, VQFP-100 |

| 文件頁(yè)數(shù): | 28/100頁(yè) |

| 文件大小: | 3284K |

| 代理商: | A3PN125-Z2VQG100I |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)當(dāng)前第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)第66頁(yè)第67頁(yè)第68頁(yè)第69頁(yè)第70頁(yè)第71頁(yè)第72頁(yè)第73頁(yè)第74頁(yè)第75頁(yè)第76頁(yè)第77頁(yè)第78頁(yè)第79頁(yè)第80頁(yè)第81頁(yè)第82頁(yè)第83頁(yè)第84頁(yè)第85頁(yè)第86頁(yè)第87頁(yè)第88頁(yè)第89頁(yè)第90頁(yè)第91頁(yè)第92頁(yè)第93頁(yè)第94頁(yè)第95頁(yè)第96頁(yè)第97頁(yè)第98頁(yè)第99頁(yè)第100頁(yè)

ProASIC3 nano DC and Switching Characteristics

Ad vance v0.2

2-19

The length of time an I/O can withstand IOSH/IOSL events depends on the junction temperature. The

reliability data below is based on a 3.3 V, 8 mA I/O setting, which is the worst case for this type of

analysis.

For example, at 110°C, the short current condition would have to be sustained for more than three

months to cause a reliability concern. The I/O design does not contain any short circuit protection,

but such protection would only be needed in extremely prolonged stress conditions.

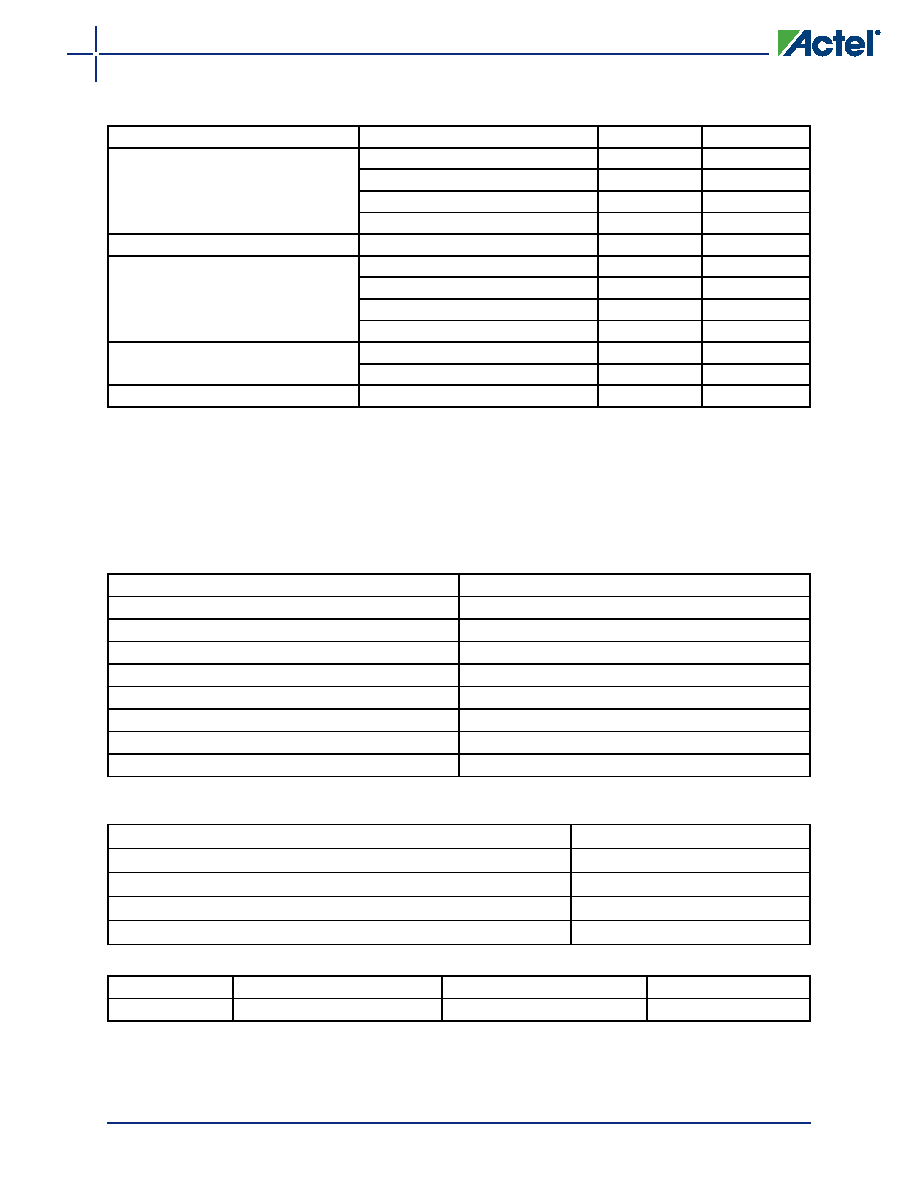

Table 2-23 I/O Short Currents IOSH/IOSL

Drive Strength

IOSL (mA)*

IOSH (mA)*

3.3 V LVTTL / 3.3 V LVCMOS

2 mA

25

27

4 mA

25

27

6 mA

51

54

8 mA

51

54

3.3 V LVCMOS Wide Range

100 A

TBD

2.5 V LVCMOS

2 mA

16

18

4 mA

16

18

6 mA

32

37

8 mA

32

37

1.8 V LVCMOS

2 mA

9

11

4 mA

17

22

1.5 V LVCMOS

2 mA

13

16

* TJ = 100°C

Table 2-24 Duration of Short Circuit Event before Failure

Temperature

Time before Failure

–40°C

> 20 years

–20°C

> 20 years

0°C

> 20 years

25°C

> 20 years

70°C

5 years

85°C

2 years

100°C

6 months

110°C

3 months

Table 2-25 Schmitt Trigger Input Hysteresis

Hysteresis Voltage Value (Typ.) for Schmitt Mode Input Buffers

Input Buffer Configuration

Hysteresis Value (typ.)

3.3 V LVTTL / LVCMOS (Schmitt trigger mode)

240 mV

2.5 V LVCMOS (Schmitt trigger mode)

140 mV

1.8 V LVCMOS (Schmitt trigger mode)

80 mV

1.5 V LVCMOS (Schmitt trigger mode)

60 mV

Table 2-26 I/O Input Rise Time, Fall Time, and Related I/O Reliability

Input Buffer

Input Rise/Fall Time (min.)

Input Rise/Fall Time (max.)

Reliability

LVTTL/LVCMOS

No requirement

10 ns *

20 years (110°C)

* The maximum input rise/fall time is related to the noise induced into the input buffer trace. If the noise is low,

then the rise time and fall time of input buffers can be increased beyond the maximum value. The longer the

rise/fall times, the more susceptible the input signal is to the board noise. Actel recommends signal integrity

evaluation/characterization of the system to ensure that there is no excessive noise coupling into input signals.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A3PN125-Z2VQG100 | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-ZVQ100I | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-ZVQ100 | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-ZVQG100I | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

| A3PN125-ZVQG100 | FPGA, 3072 CLBS, 125000 GATES, PQFP100 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A3PN125-ZVQ100 | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:ProASIC3 nano 標(biāo)準(zhǔn)包裝:152 系列:IGLOO PLUS LAB/CLB數(shù):- 邏輯元件/單元數(shù):792 RAM 位總計(jì):- 輸入/輸出數(shù):120 門數(shù):30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應(yīng)商設(shè)備封裝:289-CSP(14x14) |

| A3PN125-ZVQ100I | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:ProASIC3 nano 標(biāo)準(zhǔn)包裝:152 系列:IGLOO PLUS LAB/CLB數(shù):- 邏輯元件/單元數(shù):792 RAM 位總計(jì):- 輸入/輸出數(shù):120 門數(shù):30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應(yīng)商設(shè)備封裝:289-CSP(14x14) |

| A3PN125-ZVQG100 | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:ProASIC3 nano 標(biāo)準(zhǔn)包裝:152 系列:IGLOO PLUS LAB/CLB數(shù):- 邏輯元件/單元數(shù):792 RAM 位總計(jì):- 輸入/輸出數(shù):120 門數(shù):30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應(yīng)商設(shè)備封裝:289-CSP(14x14) |

| A3PN125-ZVQG100I | 功能描述:IC FPGA NANO 125K GATES 100-VQFP RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:ProASIC3 nano 標(biāo)準(zhǔn)包裝:152 系列:IGLOO PLUS LAB/CLB數(shù):- 邏輯元件/單元數(shù):792 RAM 位總計(jì):- 輸入/輸出數(shù):120 門數(shù):30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應(yīng)商設(shè)備封裝:289-CSP(14x14) |

| A3PN250-1VQ100 | 功能描述:IC FPGA NANO 250K GATES 100-VQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場(chǎng)可編程門陣列) 系列:ProASIC3 nano 標(biāo)準(zhǔn)包裝:152 系列:IGLOO PLUS LAB/CLB數(shù):- 邏輯元件/單元數(shù):792 RAM 位總計(jì):- 輸入/輸出數(shù):120 門數(shù):30000 電源電壓:1.14 V ~ 1.575 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 85°C 封裝/外殼:289-TFBGA,CSBGA 供應(yīng)商設(shè)備封裝:289-CSP(14x14) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。