- 您現在的位置:買賣IC網 > PDF目錄373913 > AD7703AQ (ANALOG DEVICES INC) LC2MOS 20-Bit A/D Converter PDF資料下載

參數資料

| 型號: | AD7703AQ |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | LC2MOS 20-Bit A/D Converter |

| 中文描述: | 1-CH 20-BIT DELTA-SIGMA ADC, SERIAL ACCESS, CDIP20 |

| 封裝: | CERDIP-20 |

| 文件頁數: | 8/16頁 |

| 文件大小: | 251K |

| 代理商: | AD7703AQ |

AD7703

–8–

REV. D

DIGIT AL FILT E RING

T he AD7703’s digital filter behaves like an analog filter, with a

few minor differences.

First, since digital filtering occurs after the A to D conversion

process, it can remove noise injected during the conversion

process. Analog filtering cannot do this.

On the other hand, analog filtering can remove noise superim-

posed on the analog signal before it reaches the ADC. Digital

filtering cannot do this and noise peaks riding on signals near

full scale have the potential to saturate the analog modulator

and digital filter, even though the average value of the signal is

within limits. T o alleviate this problem, the AD7703 has over-

range headroom built into the sigma-delta modulator and digital

filter which allows overrange excursions of 100 mV. If noise sig-

nals are larger than this, consideration should be given to analog

input filtering, or to reducing the gain in the input channel so

that a full-scale input (2.5 V) gives only a half-scale input to the

AD7703 (1.25 V). T his will provide an overrange capability

greater than 100% at the expense of reducing the dynamic range

by 1 bit (50%).

FILT E R CHARACT E RIST ICS

T he cutoff frequency of the digital filter is f

CLK

/409600. At the

maximum clock frequency of 4.096 MHz, the cutoff frequency

of the filter is 10 Hz and the data update rate is 4 kHz.

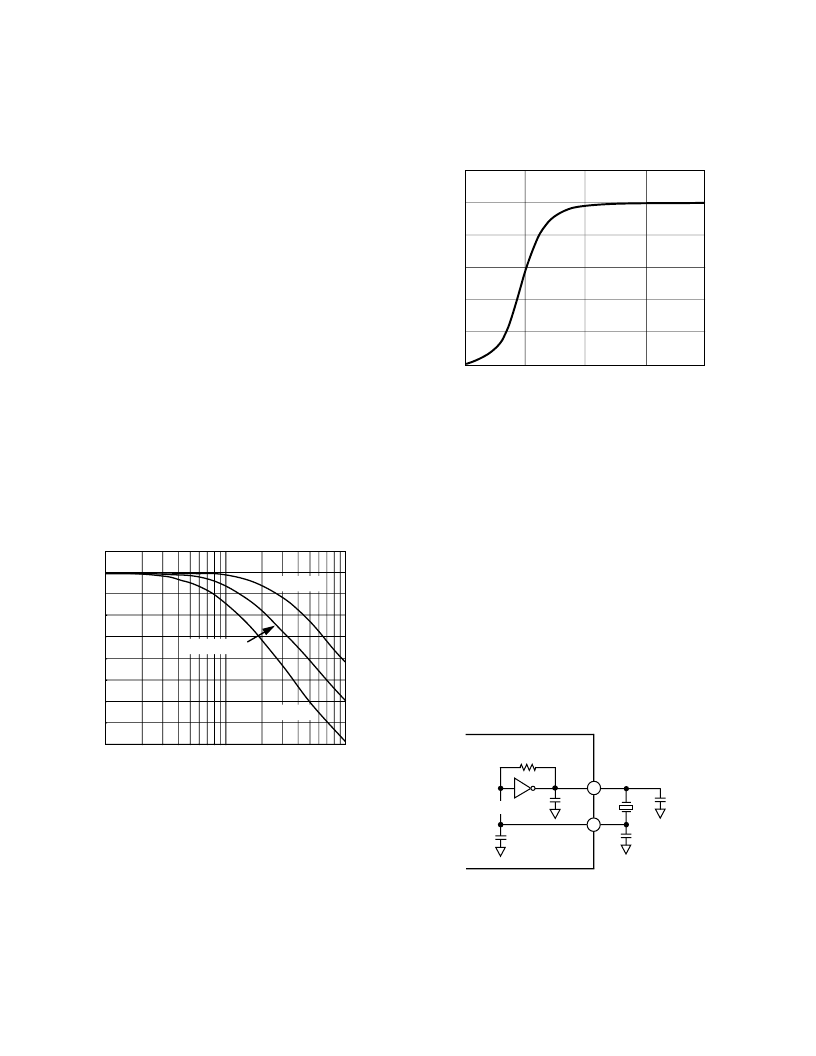

Figure 9 shows the filter frequency response. T his is a 6-pole

Gaussian response that provides 55 dB of 60 Hz rejection for a

10 Hz cutoff frequency. If the clock frequency is halved to give a

5 Hz cutoff, 60 Hz rejection is better than 90 dB.

1

10

100

FREQUENCY – Hz

20

0

–20

–40

–60

–80

–100

–120

–140

–160

G

f

CLK

= 1MHz

f

CLK

= 2MHz

f

CLK

= 4MHz

Figure 9. Frequency Response of AD7703 Filter

Since the AD7703 contains this low-pass filtering, there is a set-

tling time associated with step function inputs, and data will be

invalid after a step change until the settling time has elapsed.

T he AD7703 is, therefore, unsuitable for high speed multiplex-

ing, where channels are switched and converted sequentially at

high rates, as switching between channels can cause a step

change in the input. However, slow multiplexing of the AD7703

is possible, provided that the settling time is allowed to elapse

before data for the new channel is accessed.

T he output settling of the AD7703 in response to a step input

change is shown in Figure 10. T he Gaussian response has fast

settling with no overshoot, and the worst-case settling time to

±

0.0007% is 125 ms with a 4.096 MHz master clock frequency.

P

100

80

60

40

20

0

0

40

80

120

160

TIME – ms

Figure 10. AD7703 Step Response

USING T HE AD7703

SY ST E M DE SIGN CONSIDE RAT IONS

T he AD7703 operates differently from successive approxima-

tion ADCs or integrating ADCs. Since it samples the signal con-

tinuously, like a tracking ADC, there is no need for a start convert

command. T he 20-bit output register is updated at a 4 kHz rate,

and the output can be read at any time, either synchronously or

asynchronously.

C LOC K ING

T he AD7703 requires a master clock input, which may be an

external T T L/CMOS compatible clock signal applied to the

CLK IN pin (CLK OUT not used). Alternatively, a crystal of the

correct frequency can be connected between CLK IN and

CLK OUT , when the clock circuit will function as a crystal

controlled oscillator.

Figure 11 shows a simple model of the on-chip gate oscillator

and T able II gives some typical capacitor values to be used with

various resonators.

AD7703

C2*

C1*

R1

5M

X1

2

3

10pF

10pF

g

m

= 1500

μ

MHO

*SEE TABLE II

Figure 11. On-Chip Gate Oscillator

相關PDF資料 |

PDF描述 |

|---|---|

| AD7703AR | LC2MOS 20-Bit A/D Converter |

| AD7703BN | LC2MOS 20-Bit A/D Converter |

| AD7703BQ | LC2MOS 20-Bit A/D Converter |

| AD7703BR | ECONOLINE: REC2.2-S_DRW(Z)/H* - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- 4.5-9V, 9-18V, 18-36V, 36-72V Wide Input Range 2 : 1- UL94V-0 Package Material- Continuous Short Circiut Protection- Cost Effective- 100% Burned In- Efficiency to 84% |

| AD7703CN | LC2MOS 20-Bit A/D Converter |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7703AR | 功能描述:IC ADC 20BIT LC2MOS 20-SOIC RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7703AR-REEL | 功能描述:IC ADC 20BIT LC2MOS MONO 20-SOIC RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7703ARZ | 功能描述:IC ADC 20BIT LC2MOS 20-SOIC RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD7703BN | 功能描述:IC ADC 20BIT LC2MOS 20-DIP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 產品培訓模塊:Lead (SnPb) Finish for COTS Obsolescence Mitigation Program 標準包裝:2,500 系列:- 位數:12 采樣率(每秒):3M 數據接口:- 轉換器數目:- 功率耗散(最大):- 電壓電源:- 工作溫度:- 安裝類型:表面貼裝 封裝/外殼:SOT-23-6 供應商設備封裝:SOT-23-6 包裝:帶卷 (TR) 輸入數目和類型:- |

| AD7703BNZ | 功能描述:IC ADC 20BIT LC2MOS MONO 20DIP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 其它有關文件:TSA1204 View All Specifications 標準包裝:1 系列:- 位數:12 采樣率(每秒):20M 數據接口:并聯 轉換器數目:2 功率耗散(最大):155mW 電壓電源:模擬和數字 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-TQFP 供應商設備封裝:48-TQFP(7x7) 包裝:Digi-Reel® 輸入數目和類型:4 個單端,單極;2 個差分,單極 產品目錄頁面:1156 (CN2011-ZH PDF) 其它名稱:497-5435-6 |

發布緊急采購,3分鐘左右您將得到回復。