- 您現在的位置:買賣IC網 > PDF目錄373913 > AD7705 (Analog Devices, Inc.) 3 V/5 V, 1 mW 2-/3-Channel 16-Bit, Sigma-Delta ADCs PDF資料下載

參數資料

| 型號: | AD7705 |

| 廠商: | Analog Devices, Inc. |

| 英文描述: | 3 V/5 V, 1 mW 2-/3-Channel 16-Bit, Sigma-Delta ADCs |

| 中文描述: | 3伏/ 5伏,1毫瓦2-/3-Channel 16位Σ-Δ模數轉換器 |

| 文件頁數: | 18/32頁 |

| 文件大小: | 264K |

| 代理商: | AD7705 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁當前第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁

AD7705/AD7706

–18–

REV. A

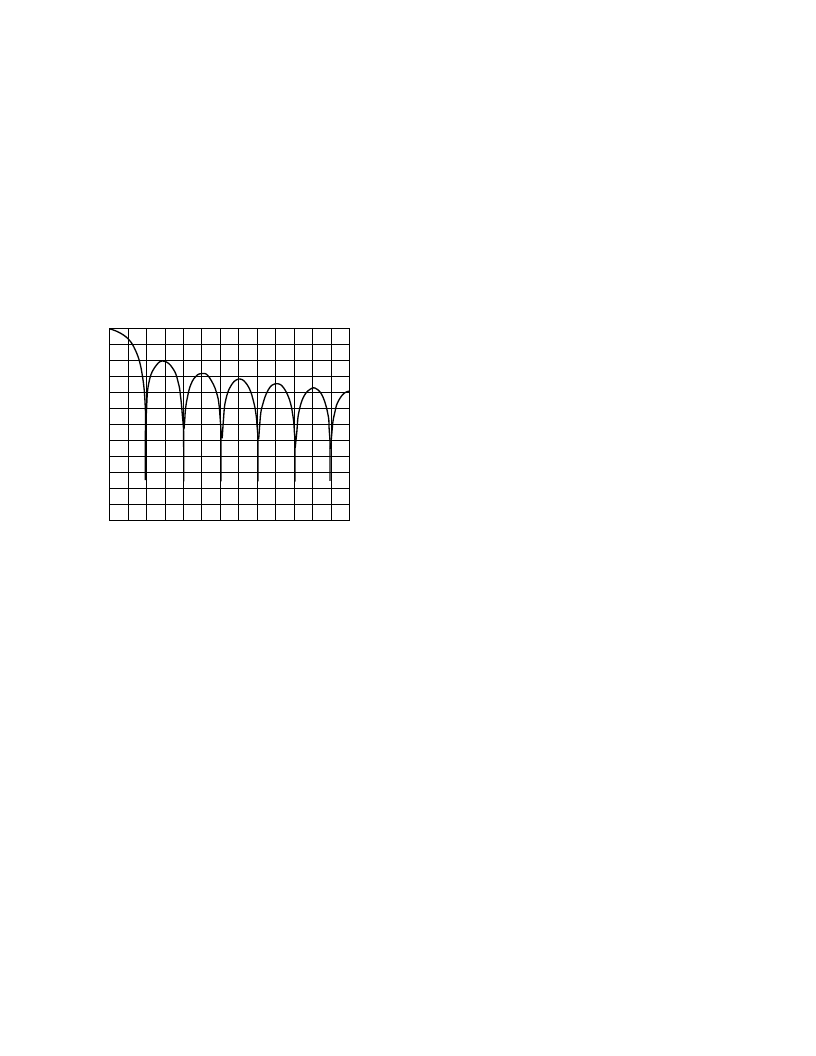

The cutoff frequency of the digital filter is determined by the

value loaded to bits FS0 to FS1 in the CLOCK Register. Pro-

gramming a different cutoff frequency via FS0 and FS1 does not

alter the profile of the filter response, it changes the frequency of

the notches. The output update of the part and the frequency of

the first notch correspond.

Since the AD7705/AD7706 contains this on-chip, low-pass

filtering, a settling time is associated with step function inputs

and data on the output will be invalid after a step change until

the settling time has elapsed. The settling time depends upon

the output rate chosen for the filter. The settling time of the

filter to a full-scale step input can be up to four times the output

data period. For a synchronized step input (using the FSYNC

function), the settling time is three times the output data period.

FREQUENCY – Hz

0

–140

–240

0

G

60

120

180

240

300

360

–20

–160

–180

–60

–100

–40

–80

–200

–220

–120

Figure 12. Frequency Response of AD7705 Filter

Post-Filtering

The on-chip modulator provides samples at a 19.2kHz output

rate with f

CLKIN

at 2.4576MHz. The on-chip digital filter deci-

mates these samples to provide data at an output rate that corre-

sponds to the programmed output rate of the filter. Since the

output data rate is higher than the Nyquist criterion, the output

rate for a given bandwidth will satisfy most application require-

ments. There may, however, be some applications which require

a higher data rate for a given bandwidth and noise performance.

Applications that need this higher data rate will require some

post-filtering following the digital filter of the AD7705/AD7706.

For example, if the required bandwidth is 7.86Hz, but the

required update rate is 100Hz, the data can be taken from the

AD7705/AD7706 at the 100Hz rate giving a –3 dB bandwidth

of 26.2Hz. Post-filtering can be applied to this to reduce the

bandwidth and output noise, to the 7.86Hz bandwidth level,

while maintaining an output rate of 100Hz.

Post-filtering can also be used to reduce the output noise from

the device for bandwidths below 13.1Hz. At a gain of 128 and

a bandwidth of 13.1Hz, the output rms noise is 450nV. This

is essentially device noise or white noise and since the input is

chopped, the noise has a primarily flat frequency response. By

reducing the bandwidth below 13.1Hz, the noise in the result-

ant passband can be reduced. A reduction in bandwidth by a

factor of 2 results in a reduction of approximately 1.25 in the

output rms noise. This additional filtering will result in a longer

settling-time.

ANALOG FILTERING

The digital filter does not provide any rejection at integer mul-

tiples of the modulator sample frequency, as outlined earlier.

However, due to the AD7705/AD7706’s high oversampling

ratio, these bands occupy only a small fraction of the spectrum

and most broadband noise is filtered. This means that the ana-

log filtering requirements in front of the AD7705/AD7706 are

considerably reduced versus a conventional converter with no

on-chip filtering. In addition, because the part’s common-mode

rejection performance of 100dB extends out to several kHz,

common-mode noise in this frequency range will be substan-

tially reduced.

Depending on the application, however, it may be necessary to

provide attenuation prior to the AD7705/AD7706 in order to

eliminate unwanted frequencies from these bands which the

digital filter will pass. It may also be necessary in some applica-

tions to provide analog filtering in front of the AD7705/AD7706

to ensure that differential noise signals outside the band of inter-

est do not saturate the analog modulator.

If passive components are placed in front of the AD7705/AD7706

in unbuffered mode, care must be taken to ensure that the

source impedance is low enough not to introduce gain errors in

the system. This significantly limits the amount of passive anti-

aliasing filtering which can be provided in front of the AD7705/

AD7706 when it is used in unbuffered mode. However, when

the part is used in buffered mode, large source impedances will

simply result in a small dc offset error (a 10k

source resistance

will cause an offset error of less than 10

μ

V). Therefore, if the

system requires any significant source impedances to provide

passive analog filtering in front of the AD7705/AD7706, it is

recommended that the part be operated in buffered mode.

CALIBRATION

The AD7705/AD7706 provides a number of calibration options

which can be programmed via the MD1 and MD0 bits of the

Setup Register. The different calibration options are outlined in

the Setup Register and Calibration Sequences sections. A cali-

bration cycle may be initiated at any time by writing to these

bits of the Setup Register. Calibration on the AD7705/AD7706

removes offset and gain errors from the device. A calibration

routine should be initiated on the device whenever there is a

change in the ambient operating temperature or supply voltage.

It should also be initiated if there is a change in the selected

gain, filter notch or bipolar/unipolar input range.

The AD7705/AD7706 offers self-calibration and system calibra-

tion facilities. For full calibration to occur on the selected chan-

nel, the on-chip microcontroller must record the modulator

output for two different input conditions. These are “zero-

scale” and “full-scale” points. These points are derived by

performing a conversion on the different input voltages provided

to the input of the modulator during calibration. As a result, the

accuracy of the calibration can only be as good as the noise level

that it provides in normal mode. The result of the “zero-scale”

calibration conversion is stored in the Zero-Scale Calibration

Register while the result of the “full-scale” calibration conver-

sion is stored in the Full-Scale Calibration Register. With these

readings, the microcontroller can calculate the offset and the

gain slope for the input-to-output transfer function of the con-

verter. Internally, the part works with a resolution of 33 bits to

determine its conversion result of 16 bits.

相關PDF資料 |

PDF描述 |

|---|---|

| AD7705BN | ECONOLINE: REC2.2-S_DR/H1 - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- UL94V-0 Package Material- Continuous Short Circiut Protection- Internal SMD design- 100% Burned In- Efficiency to 75% |

| AD7705BR | ECONOLINE: REC2.2-S_DRW(Z)/H* - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- 4.5-9V, 9-18V, 18-36V, 36-72V Wide Input Range 2 : 1- UL94V-0 Package Material- Continuous Short Circiut Protection- Cost Effective- 100% Burned In- Efficiency to 84% |

| AD7705BRU | 3 V/5 V, 1 mW 2-/3-Channel 16-Bit, Sigma-Delta ADCs |

| AD7706 | 3 V/5 V, 1 mW 2-/3-Channel 16-Bit, Sigma-Delta ADCs |

| AD7706BN | ECONOLINE: REC2.2-S_DRW(Z)/H* - 2.2W DIP Package- 1kVDC Isolation- Regulated Output- 4.5-9V, 9-18V, 18-36V, 36-72V Wide Input Range 2 : 1- UL94V-0 Package Material- Continuous Short Circiut Protection- Cost Effective- 100% Burned In- Efficiency to 84% |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD7705_06 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, 1 mW, 2-/3-Channel, 16-Bit, Sigma-Delta ADCs |

| AD7705BN | 功能描述:IC ADC 16BIT 2CH 16-DIP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:16 采樣率(每秒):45k 數據接口:串行 轉換器數目:2 功率耗散(最大):315mW 電壓電源:模擬和數字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應商設備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數目和類型:2 個單端,單極 |

| AD7705BNZ | 功能描述:IC ADC 16BIT 2CH 16-DIP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 其它有關文件:TSA1204 View All Specifications 標準包裝:1 系列:- 位數:12 采樣率(每秒):20M 數據接口:并聯 轉換器數目:2 功率耗散(最大):155mW 電壓電源:模擬和數字 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-TQFP 供應商設備封裝:48-TQFP(7x7) 包裝:Digi-Reel® 輸入數目和類型:4 個單端,單極;2 個差分,單極 產品目錄頁面:1156 (CN2011-ZH PDF) 其它名稱:497-5435-6 |

| AD7705BNZ1 | 制造商:AD 制造商全稱:Analog Devices 功能描述:3 V/5 V, 1 mW, 2-/3-Channel, 16-Bit, Sigma-Delta ADCs |

| AD7705BR | 功能描述:IC ADC 16BIT 2CH 16-SOIC RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1,000 系列:- 位數:12 采樣率(每秒):300k 數據接口:并聯 轉換器數目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應商設備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數目和類型:1 個單端,單極;1 個單端,雙極 |

發布緊急采購,3分鐘左右您將得到回復。