- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄373914 > AD7715ARU-3 (ANALOG DEVICES INC) 3 V/5 V, 450 uA 16-Bit, Sigma-Delta ADC PDF資料下載

參數(shù)資料

| 型號(hào): | AD7715ARU-3 |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | 3 V/5 V, 450 uA 16-Bit, Sigma-Delta ADC |

| 中文描述: | 1-CH 16-BIT DELTA-SIGMA ADC, SERIAL ACCESS, PDSO16 |

| 封裝: | MO-153AB, TSSOP-16 |

| 文件頁數(shù): | 10/31頁 |

| 文件大小: | 474K |

| 代理商: | AD7715ARU-3 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁當(dāng)前第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁

REV. C

AD7715

–10–

Setup Register (RS1, RS0 = 0, 1); Power On/Reset Status: 28Hex

The Setup Register is an eight-bit register from which data can either be read or to which data can be written. This register controls

the setup which the device is to operate in such as the calibration mode, output rate, unipolar/bipolar operation etc. Table III out-

lines the bit designations for the Setup Register.

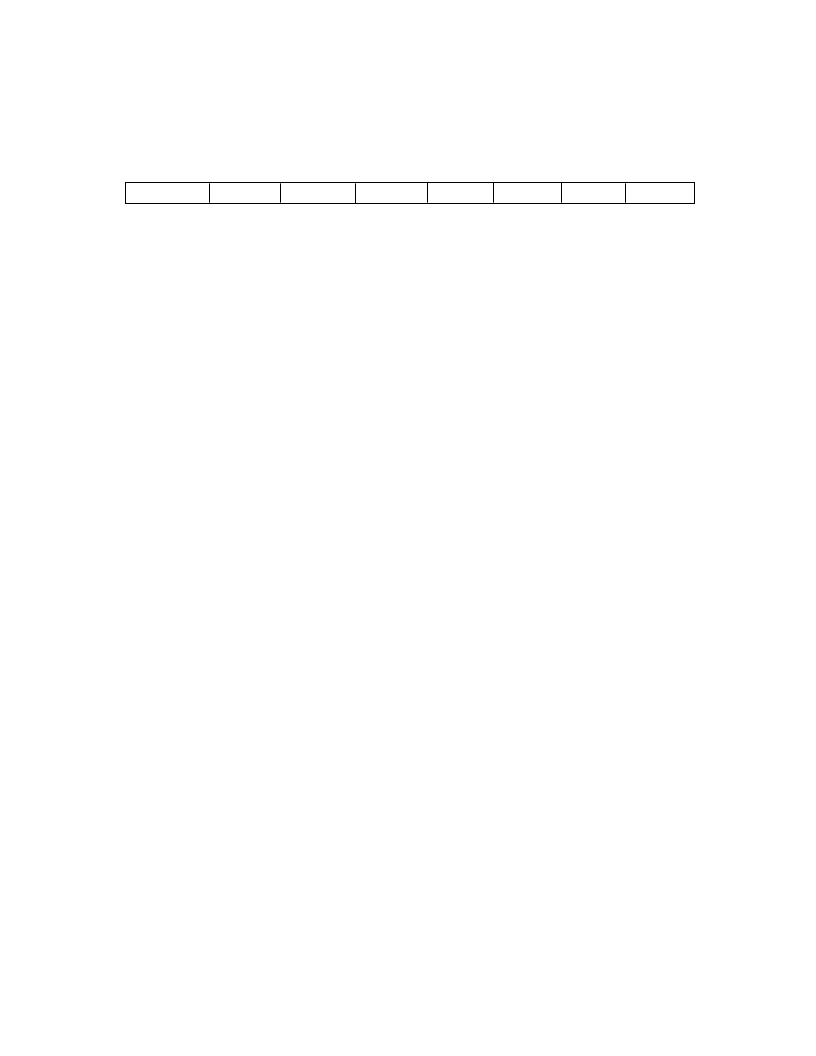

Table III. Setup Register

MD1 MD0 CLK FS1 FS0

B

/U BUF FSYNC

MD1

0

MD0

0

Operating Mode

Normal Mode; this is the normal mode of operation of the device whereby the device is performing normal

conversions. This is the default condition of these bits after Power-On or RESET.

Self-Calibration; this activates self-calibration on the part. This is a one step calibration sequence and when

complete the part returns to Normal Mode with MD1 and MD0 returning to 0, 0. The

DRDY

output or bit

goes high when calibration is initiated and returns low when this self-calibration is complete and a new valid

word is available in the data register. The zero-scale calibration is performed at the selected gain on internally

shorted (zeroed) inputs and the full-scale calibration is performed at the selected gain on an internally

generated V

REF

/Selected Gain.

Zero-Scale System Calibration; this activates zero-scale system calibration on the part. Calibration is per-

formed at the selected gain on the input voltage provided at the analog input during this calibration sequence.

This input voltage should remain stable for the duration of the calibration. The

DRDY

output or bit goes

high when calibration is initiated and returns low when this zero-scale calibration is complete and a new valid

word is available in the data register. At the end of the calibration, the part returns to Normal Mode with

MD1 and MD0 returning to 0, 0.

Full-Scale System Calibration; this activates full-scale system calibration on the part. Calibration is per-

formed at the selected gain on the input voltage provided at the analog input during this calibration sequence.

This input voltage should remain stable for the duration of the calibration. Once again, the

DRDY

output or

bit goes high when calibration is initiated and returns low when this full-scale calibration is complete and a

new valid word is available in the data register. At the end of the calibration, the part returns to Normal

Mode with MD1 and MD0 returning to 0, 0.

Clock Bit. This bit should be set in accordance with the operating frequency of the AD7715. If the device has

a master clock frequency of 2.4576MHz, then this bit should be set to a 1. If the device has a master clock

frequency of 1MHz, then this bit should be set to a 0. This bit sets up the correct scaling currents for a given

master clock and also chooses (along with FS1 and FS0) the output update rate for the device. If this bit is

not set correctly for the master clock frequency of the device, then the device may not operate to specifica-

tion. The default value for this bit after power-on or RESET is 1.

Filter Selection Bits. Along with the CLK bit, FS1 and FS0 determine the output update rate, filter first

notch and –3 dB frequency as outlined in Table IV. The on-chip digital filter provides a Sinc

3

(or (Sinx/x)

3

)

filter response. In association with the gain selection, it also determines the output noise (and hence the

resolution) of the device. Changing the filter notch frequency, as well as the selected gain, impacts resolution.

Tables V through XII show the effect of the filter notch frequency and gain on the output noise and effective

resolution of the part. The output data rate (or effective conversion time) for the device is equal to the fre-

quency selected for the first notch of the filter. For example, if the first notch of the filter is selected at 50Hz

then a new word is available at a 50 Hz rate or every 20ms. If the first notch is at 500Hz, a new word is

available every 2ms. The default value for these bits is 1, 0.

The settling-time of the filter to a full-scale step input change is worst case 4

×

1/(output data rate). For

example, with the first filter notch at 50Hz, the settling time of the filter to a full-scale step input change is

80ms max. If the first notch is at 500Hz, the settling time of the filter to a full-scale input step is 8ms max.

This settling-time can be reduced to 3

×

1/(output data rate) by synchronizing the step input change to a

reset of the digital filter. In other words, if the step input takes place with the FSYNC bit high, the settling-

time time will be 3

×

1/(output data rate) from when FSYNC returns low.

The –3 dB frequency is determined by the programmed first notch frequency according to the relationship:

filter –3 dB frequency = 0.262

×

filter first notch frequency.

0

1

1

0

1

1

CLK

FS1, FS0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| AD7715ARU-5 | AB 4C 4#12 PIN RECP |

| AD7715AN-3 | 3 V/5 V, 450 uA 16-Bit, Sigma-Delta ADC |

| AD7715AN-5 | 3 V/5 V, 450 uA 16-Bit, Sigma-Delta ADC |

| AD7715AR-3 | 3 V/5 V, 450 uA 16-Bit, Sigma-Delta ADC |

| AD7715AR-5 | 3 V/5 V, 450 uA 16-Bit, Sigma-Delta ADC |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| AD7715ARU-3REEL | 功能描述:IC ADC 16BIT SIGMA-DELTA 16TSSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:- 位數(shù):16 采樣率(每秒):45k 數(shù)據(jù)接口:串行 轉(zhuǎn)換器數(shù)目:2 功率耗散(最大):315mW 電壓電源:模擬和數(shù)字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應(yīng)商設(shè)備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數(shù)目和類型:2 個(gè)單端,單極 |

| AD7715ARU-3REEL7 | 功能描述:IC ADC 16BIT SIGMA-DELTA 16TSSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:- 位數(shù):16 采樣率(每秒):45k 數(shù)據(jù)接口:串行 轉(zhuǎn)換器數(shù)目:2 功率耗散(最大):315mW 電壓電源:模擬和數(shù)字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應(yīng)商設(shè)備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數(shù)目和類型:2 個(gè)單端,單極 |

| AD7715ARU-5 | 功能描述:IC ADC 16BIT SIGMA-DELTA 16TSSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:- 位數(shù):12 采樣率(每秒):300k 數(shù)據(jù)接口:并聯(lián) 轉(zhuǎn)換器數(shù)目:1 功率耗散(最大):75mW 電壓電源:單電源 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:24-SOIC(0.295",7.50mm 寬) 供應(yīng)商設(shè)備封裝:24-SOIC 包裝:帶卷 (TR) 輸入數(shù)目和類型:1 個(gè)單端,單極;1 個(gè)單端,雙極 |

| AD7715ARU-5REEL | 功能描述:IC ADC 16BIT SIGMA-DELTA 16TSSOP RoHS:否 類別:集成電路 (IC) >> 數(shù)據(jù)采集 - 模數(shù)轉(zhuǎn)換器 系列:- 標(biāo)準(zhǔn)包裝:1,000 系列:- 位數(shù):16 采樣率(每秒):45k 數(shù)據(jù)接口:串行 轉(zhuǎn)換器數(shù)目:2 功率耗散(最大):315mW 電壓電源:模擬和數(shù)字 工作溫度:0°C ~ 70°C 安裝類型:表面貼裝 封裝/外殼:28-SOIC(0.295",7.50mm 寬) 供應(yīng)商設(shè)備封裝:28-SOIC W 包裝:帶卷 (TR) 輸入數(shù)目和類型:2 個(gè)單端,單極 |

| AD7715ARU-5REEL7 | 制造商:Analog Devices 功能描述:ADC Single Delta-Sigma 19.2ksps 16-bit Serial 16-Pin TSSOP T/R |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。