- 您現在的位置:買賣IC網 > PDF目錄373916 > AD774BBD (ANALOG DEVICES INC) Complete 12-Bit A/D Converters PDF資料下載

參數資料

| 型號: | AD774BBD |

| 廠商: | ANALOG DEVICES INC |

| 元件分類: | ADC |

| 英文描述: | Complete 12-Bit A/D Converters |

| 中文描述: | 1-CH 12-BIT SUCCESSIVE APPROXIMATION ADC, PARALLEL ACCESS, CDIP28 |

| 封裝: | HERMETIC SEALED, CERAMIC, DIP-28 |

| 文件頁數: | 10/12頁 |

| 文件大小: | 247K |

| 代理商: | AD774BBD |

REV. C

–10–

AD674B/AD774B

STANDALONE MODE

“

Standalone

”

mode is useful in systems with dedicated input

ports available and thus not requiring full bus interface capabil-

ity. Standalone mode applications are generally able to issue

conversion start commands more precisely than full-control

mode, resulting in improved accuracy.

CE and 12/

8

are wired HIGH,

CS

and A

0

are wired LOW, and

conversion is controlled by R/

C

. The three-state buffers are

enabled when R/

C

is HIGH and a conversion starts when R/

C

goes LOW. This gives rise to two possible control signals

—

a

high pulse or a low pulse. Operation with a low pulse is shown

in Figure 4a. In this case, the outputs are forced into the high

impedance state in response to the falling edge of R/

C

and

return to valid logic levels after the conversion cycle is completed.

The STS line goes HIGH 200 ns after R/C goes LOW and

returns low 600 ns after data is valid.

If conversion is initiated by a high pulse as shown in Figure 4b,

the data lines are enabled during the time when R/

C

is HIGH.

The falling edge of R/

C

starts the next conversion, and the data

lines return to three-state (and remain three-state) until the next

high pulse of R/

C

.

CONVERSION TIMING

Once a conversion is started, the STS line goes HIGH. Convert

start commands will be ignored until the conversion cycle is

complete. The output data buffers can be enabled up to 1.2

μ

s

prior to STS going LOW. The STS line will return LOW at the

end of the conversion cycle.

The register control inputs, A

0

and 12/

8

, control conversion

length and data format. If a conversion is started with A

0

LOW,

a full 12-bit conversion cycle is initiated. If A

0

is HIGH during a

convert start, a shorter 8-bit conversion cycle results.

During data read operations, A

0

determines whether the three-

state buffers containing the 8 MSBs of the conversion result

(A

0

= 0) or the 4 LSBs (A

0

= 1) are enabled. The 12/

8

pin

determines whether the output data is to be organized as two

8-bit words (12/

8

tied LOW) or a single 12-bit word (12/

8

tied

HIGH). In the 8-bit mode, the byte addressed when A

0

is high

contains the 4 LSBs from the conversion followed by four trail-

ing zeroes. This organization allows the data lines to be over-

lapped for direct interface to 8-bit buses without the need for

external three-state buffers.

GENERAL A/D CONVERTER INTERFACE

CONSIDERATIONS

A typical A/D converter interface routine involves several opera-

tions. First, a write to the ADC address initiates a conversion.

The processor must then wait for the conversion cycle to com-

plete, since most integrated circuit ADCs take longer than one

instruction cycle to complete a conversion. Valid data can, of

course, only be read after the conversion is complete. The

AD674B and AD774B provide an output signal (STS) which

indicates when a conversion is in progress. This signal can be

polled by the processor by reading it through an external three-

state buffer (or other input port). The STS signal can also

generate an interrupt upon completion of conversion if the sys-

tem timing requirements are critical and the processor has other

tasks to perform during the ADC conversion cycle. Another

possible time-out method is to assume that the ADC will take its

maximum conversion time to convert, and insert a sufficient

number of

“

no-op

”

instructions to ensure that this amount of

processor time is consumed.

Once conversion is complete, the data can be read. For convert-

ers with more data bits than are available on the bus, a choice of

data formats is required, and multiple read operations are

needed. The AD674B and AD774B include internal logic to

permit direct interface to 8-bit and 16-bit data buses, selected

by the 12/

8

input. In 16-bit bus applications (12/

8

high) the

data lines (DB11 through DB0) may be connected to either the

12 most significant or 12 least significant bits of the data bus.

The remaining 4 bits should be masked in software. The inter-

face to an 8-bit data bus (12/

8

low) is done in a left-justified for-

mat. The even address (A

0

low) contains the 8 MSBs (DB11

through DB4). The odd address (A

0

high) contains the 4 LSBs

(DB3 through DB0) in the upper half of the byte, followed by

four trailing zeroes, thus eliminating bit masking instructions.

It is not possible to rearrange the output data lines for right-jus-

tified 8-bit bus interface.

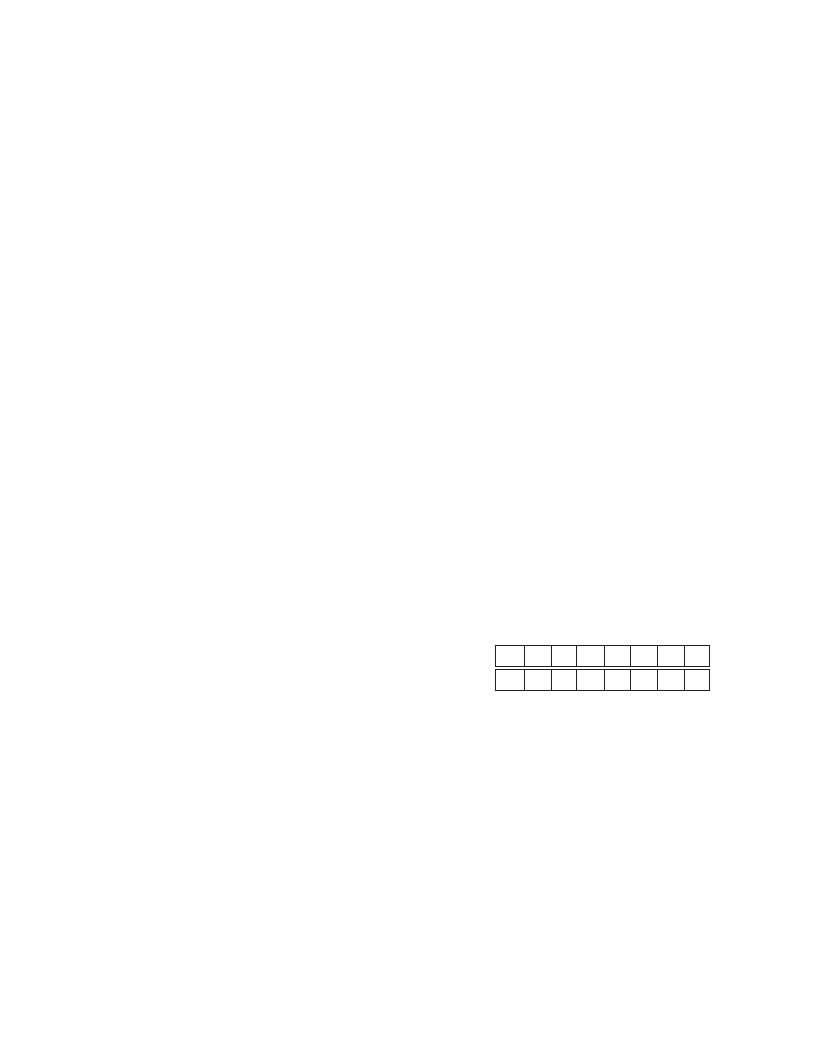

DB11

DB9

DB8

DB7

DB6

DB5

DB4

DB3

DB2

DB1

DB0

(LSB)

0

0

0

0

D7

D0

XXX0

(EVEN ADDR)

XXX1

(ODD ADDR)

Figure 10. Data Format for 8-Bit Bus

相關PDF資料 |

PDF描述 |

|---|---|

| AD774BJN | Complete 12-Bit A/D Converters |

| AD774BTD | Complete 12-Bit A/D Converters |

| AD774BKN | Complete 12-Bit A/D Converters |

| AD774BKR | Complete 12-Bit A/D Converters |

| AD7750 | Product-to-Frequency Converter(乘積-頻率轉換器) |

相關代理商/技術參數 |

參數描述 |

|---|---|

| AD774BBR | 制造商:Analog Devices 功能描述:ADC Single SAR 12-bit Parallel 28-Pin SOIC W 制造商:Rochester Electronics LLC 功能描述:IC, MONO 12-BIT ADC IC - Bulk |

| AD774BBRZ | 功能描述:IC ADC 12BIT W/BUFF REF 28SOIC RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 其它有關文件:TSA1204 View All Specifications 標準包裝:1 系列:- 位數:12 采樣率(每秒):20M 數據接口:并聯 轉換器數目:2 功率耗散(最大):155mW 電壓電源:模擬和數字 工作溫度:-40°C ~ 85°C 安裝類型:表面貼裝 封裝/外殼:48-TQFP 供應商設備封裝:48-TQFP(7x7) 包裝:Digi-Reel® 輸入數目和類型:4 個單端,單極;2 個差分,單極 產品目錄頁面:1156 (CN2011-ZH PDF) 其它名稱:497-5435-6 |

| AD774BJN | 功能描述:IC ADC 12BIT W/BUFF REF 28-DIP RoHS:否 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD774BJNZ | 功能描述:IC ADC 12BIT W/BUFF REF 28DIP RoHS:是 類別:集成電路 (IC) >> 數據采集 - 模數轉換器 系列:- 標準包裝:1 系列:- 位數:14 采樣率(每秒):83k 數據接口:串行,并聯 轉換器數目:1 功率耗散(最大):95mW 電壓電源:雙 ± 工作溫度:0°C ~ 70°C 安裝類型:通孔 封裝/外殼:28-DIP(0.600",15.24mm) 供應商設備封裝:28-PDIP 包裝:管件 輸入數目和類型:1 個單端,雙極 |

| AD774BJR | 制造商:AD 制造商全稱:Analog Devices 功能描述:Complete 12-Bit A/D Converters |

發布緊急采購,3分鐘左右您將得到回復。